# STC11F/10Fxx series MCU STC11L/10Lxx series MCU Data Sheet

# Content

| Chapter 1. Introduction                                                                                                            | 3  |

|------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.1 Features                                                                                                                       | 3  |

| 1.2 Block diagram                                                                                                                  | 4  |

| 1.3 Pin Configurations                                                                                                             | 5  |

| 1.4 Pin Descriptions                                                                                                               | 6  |

| 1.5 Pin Drawings                                                                                                                   |    |

| Chapter 2. CLOCK, POWER MANAGENMENT, RESET                                                                                         |    |

| 2.1 Clock Network                                                                                                                  |    |

| 2.2 Power Management                                                                                                               |    |

| 2.2.1 Idle Mode                                                                                                                    |    |

| 2.2.2 Slow Down Mode                                                                                                               | 11 |

| 2.2.3 Power Down (PD) Mode                                                                                                         | 12 |

| 2.2.3 Power Down (PD) Mode 2.3 RESET Control 2.3.1 Reset pin 2.3.2 Power-On Reset (POR) 2.3.3 Watch-Dog-Timer 2.3.4 Software RESET | 12 |

| 2.3.1 Reset pin                                                                                                                    | 12 |

| 2.3.2 Power-On Reset (POR)                                                                                                         | 12 |

| 2.3.3 Watch-Dog-Timer                                                                                                              | 12 |

| 2.3.4 Software RESET                                                                                                               | 13 |

| 2.3.5 MAX810 power-on-reset delay                                                                                                  | 13 |

| Chapter 3. Memory Organization                                                                                                     | 14 |

| 3.1 Program Flash Memory                                                                                                           | 14 |

| 3.2 Data Memory.                                                                                                                   | 15 |

| 3.2.1 On-chip Scratch-Pad RAM                                                                                                      | 15 |

| 3.2.2 Auxiliary RAM                                                                                                                | 15 |

| 3.2.3 External RAM                                                                                                                 | 15 |

| 3.2.4 Special Function Register for RAM                                                                                            | 15 |

| Chapter 4. Configurable I/O Ports                                                                                                  | 20 |

| 4.1 I/O Port Configurations                                                                                                        | 20 |

| 4.1.1 Quasi-bidirectional I/O                                                                                                      | 20 |

| 4.1.2 Push-pull Output                                                                                                             | 21 |

| 4.1.3 Input-only Mode                                                                                                              |    |

| 4.1.4 Open-drain Output                                                                                                            |    |

| 4.2 I/O Port Registers                                                                                                             | 22 |

| Chapter 5 Instruction System                                                                                                       | 24 |

| 5.1 Special Function Registers                                                                                                     |    |

| 5.2 Addressing Modes                                                                                                               |    |

| 5.3 Instruction Set Summary                                                                                                        |    |

| Chapter 6. Interrupt                                     | 33           |

|----------------------------------------------------------|--------------|

| 6.1 Interrupt Structure                                  | 34           |

| 6.2 Interrupt Register                                   | 35           |

| 6.3 Interrupt Priorities                                 | 37           |

| 6.4 How Interrupts Are Handled                           | 37           |

| 6.5 External Interrupts                                  | 38           |

| 6.6 Response Time                                        | 39           |

| Chapter 7. Timer/Counter 0/1                             | 40           |

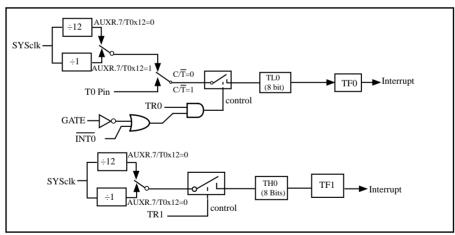

| 7.1 Timer/Counter 0 Mode of Operation                    |              |

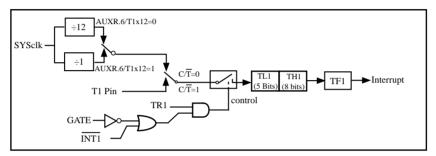

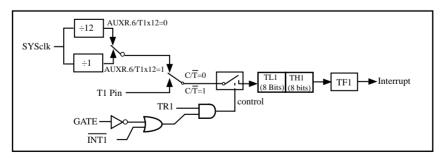

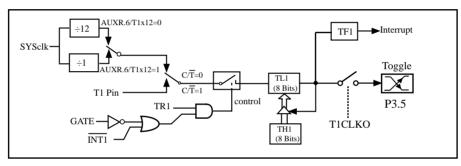

| 7.2 Timer/Counter 1 Mode of Operation                    | 45           |

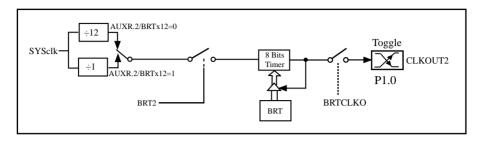

| 7.3 Baud Rate Generator and Programmable Clock Output of | on P1.0 . 47 |

| Chapter 8. UART with enhanced function                   | 48           |

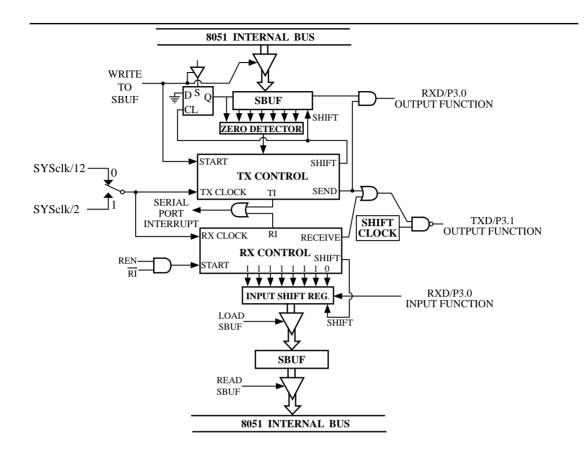

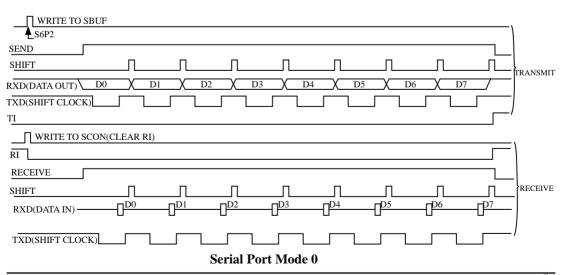

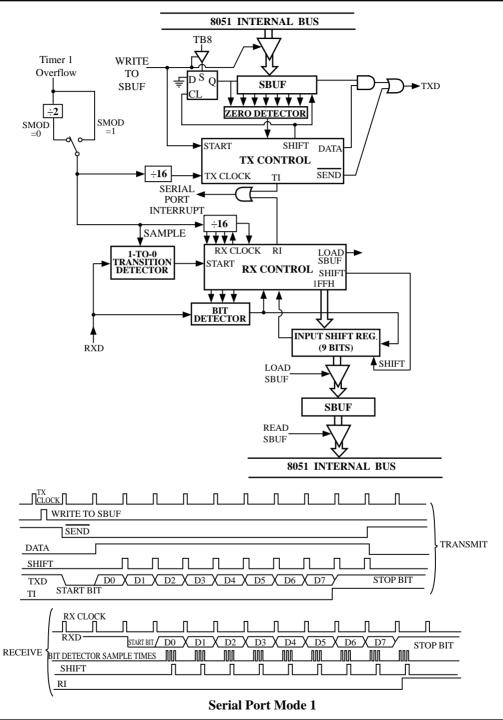

| 8.1 UART Mode of Operation                               |              |

| 8.2 Frame Error Detection                                |              |

| 8.3 Multiprocessor Communications                        | 58           |

| 8.4 Automatic Address Recognition                        |              |

| 8.5 Buad Rates                                           | 61           |

| Chapter 9 In System Programming (ISP)/In Application     |              |

| Chapter 10 STC10/11 xx series Selection Table            | 0            |

|                                                          |              |

## **Chapter 1. Introduction**

STC11F/10Fxx series are a single-chip microcontroller based on a high performance 1T architecture 80C51 CPU, which is produced by STC MCU Limited. With the enhanced kernel, STC11F/10Fxx series execute instructions in 1~6 clock cycles (about 6~7 times the rate of a standard 8051 device), and have an fully compatible instruction set with industrial-standard 80C51 series microcontroller. In-System-Programming (ISP) and In-Application-Programming (IAP) support the users to upgrade the program and data in system. ISP allows the user to download new code without removing the microcontroller from the actual end product; IAP means that the device can write non-valatile data in Flash memory while the application program is running. The STC11F/10Fxx series retain all features of the standard 80C51. In addition, the STC11F/10Fxx series have a extra I/O port (P4), a 6-sources, 2-priority-level interrupt structure, on-chip crystal oscillator, and a one-time enabled Watchdog Timer.

#### 1.1 Features

- Enhanced 80C51 Central Processing Unit, 1T per machine cycle, faster 6~7 times than the rate of a standard 8051.

- Operating voltage range: 5.5~4.1V/3.7V or 2.1V/2.4V ~ 3.6V (STC11L/10Lxx series)

- Operating frequency range: 0-35MHz, is equivalent to standard 8051:0~420MHZ

- On-chip 4/8/12/14/16/20/32/40/48/52/56/62K Flash program memory with flexible ISP/IAP capability,

- On-chip 1280/512/256 byte RAM

- · Be capable of addressing up to 64K byte of external RAM

- Dual Data Pointer (DPTR) to speed up data movement

- Code protection for flash memory access

- two 16-bit timer/counter, as the same as Timer0/Timer1 of standard 8051, one BRT(Baud-rate-generator)

- 6 vector-address, 2 level priority interrupt capability

- One enhanced UART with hardware address-recognition, frame-error detection function, and with self baudrate generator.

- One 15 bits Watch-Dog-Timer with 8-bit pre-scaler (one-time-enabled)

- Simple internal RC oscillator

- Three power management modes: idle mode, slow down mode and power-down mode

- Power down mode can be woken-up by INT0/P3.0 pin, INT1/P3.3 pin, T0/P3.4, T1/P3.5, RXD/P3.0 pin (or RXD/P1.6 pin)

- Maximum 40 programmable I/O ports are available

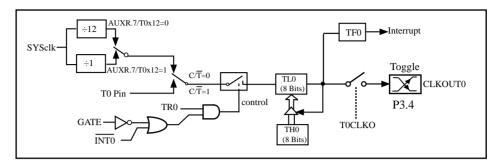

- Programable clock output Function. T0 output the clock on P3.4, T1 output the clock on P3.5, BRT output the clock on P1.0.

- Five package type: LQFP-44, PDIP-40, PLCC-44, QFN-40

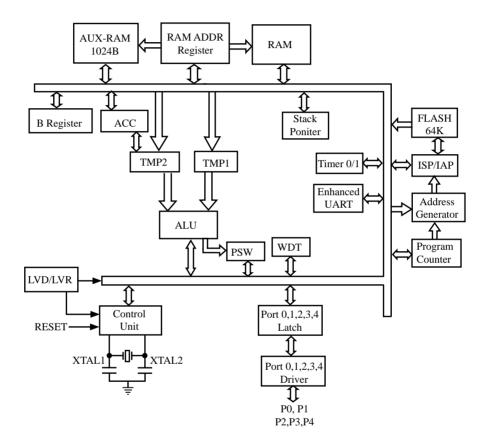

# 1.2 Block diagram

The CPU kernel of STC11/10Fxx series are fully compatible to the standard 8051 microcontroller, maintains all instruction mnemonics and binary compatibility. With some great architecture enhancements, STC11/10Fxx series execute the fastest instructions per clock cycle. Improvement of individual programs depends on the actual instructions used.

STC11/10Fxx Block Diagram

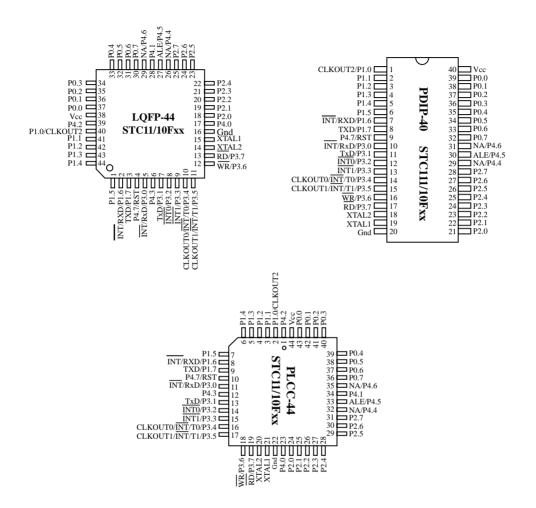

# 1.3 Pin Configurations

# 1.4 Pin Descriptions

| MNEMONIC     | LQFP44 | PDIP40 | PLCC44 | DESCRIPTION                                                             |

|--------------|--------|--------|--------|-------------------------------------------------------------------------|

| P0.0 ~ P0.7  | 30-37  | 32-39  | 36~43  | Port0 : Port0 is an 8-bit bi-directional I/O port with pull-            |

|              |        |        |        | up resistance. Except being as GPIO, Port 0 is also the                 |

|              |        |        |        | multiplexed low-order address and data bus during accesses              |

|              |        |        |        | to external program and data memory.                                    |

|              |        |        |        |                                                                         |

| P1.0 ~ P1.7  | 40~44  | 1-8    | 2~9    | Port1 : General-purposed I/O with weak pull-up resistance               |

|              | 1~3    |        |        | inside. When 1s are written into Port1, the strong output               |

|              |        |        |        | driving CMOS only turn-on two period and then the weak                  |

|              |        |        |        | pull-up resistance keep the port high.                                  |

| P2.0 ~ P2.7  | 18-25  | 21-28  | 24~31  | Port2: Port2 is an 8-bit bi-directional I/O port with pull-             |

|              |        |        |        | up resistance. Except being as GPIO, Port2 emits the high-              |

|              |        |        |        | order address byte during accessing to external program and             |

|              |        |        |        | data memory.                                                            |

| P3.0 ~ P3.7  | 5      | 10-17  | 11     | Port3 : General-purposed I/O with weak pull-up resistance               |

|              | 7~13   |        | 13~19  | inside. When 1s are written into Port1, the strong output               |

|              |        |        |        | driving CMOS only turn-on two period and then the weak                  |

|              |        |        |        | pull-up resistance keep the port high. Port3 also serves the            |

|              |        |        |        | functions of various special features .                                 |

| P4.0~P4.3    |        |        |        | Port4 : Port4 are extended I/O ports such like Port1.                   |

| P4.0         | 17     |        | 23     |                                                                         |

| P4.1         | 28     |        | 34     |                                                                         |

| P4.2         | 39     |        | 1      |                                                                         |

| P4.3         | 6      |        | 12     |                                                                         |

| RST/P4.7     | 4      | 9      | 10     | RESET: A high on this pin for at least two machine cycles               |

| P4.6         | 29     | 31     | 35     | will reset the device.                                                  |

| P4.0<br>P4.4 | 29     | 29     | 32     |                                                                         |

| ALE/P4.5     | 27     | 30     | 33     | Address I state Freehless It is soonal free sectional data section.     |

| ALE/P4.5     | 21     | 30     | 33     | Address Latch Enable: It is used for external data memory cycles (MOVX) |

| XTAL1        | 15     | 19     | 21     | Crystal 1: Input to the inverting oscillator amplifier.Receives         |

|              |        |        |        | the external oscillator signal when an external oscillator is           |

|              |        |        |        | used.                                                                   |

| XTAL2        | 14     | 18     | 20     | Crystal 2: Output from the inverting amplifier. This pin                |

|              |        |        |        | should be floated when an external oscillator is used.                  |

| VCC          | 38     | 40     | 44     | Power                                                                   |

| Gnd          | 16     | 20     | 22     | Ground                                                                  |

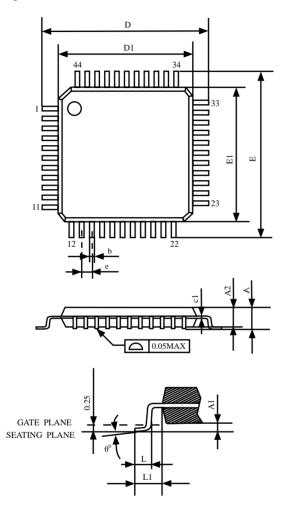

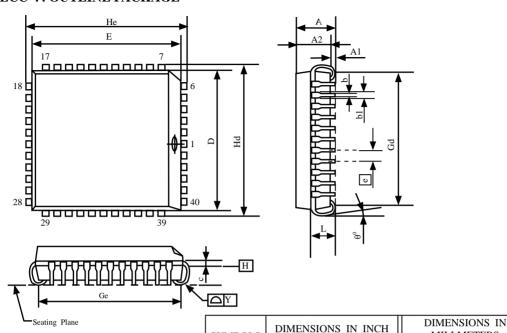

# 1.5 Pin Package Drawings

## **LQFP-44 OUTLINE PACKAGE**

| VARIATIONS     | (ALL DIME | NSIONS SHO    | OWN IN MM |

|----------------|-----------|---------------|-----------|

| SYMBOLS        | MIN.      | NOM           | MAX.      |

| A              | -         | -             | 1.60      |

| A1             | 0.05      | -             | 0.15      |

| A2             | 1.35      | 1.40          | 1.45      |

| c1             | 0.09      | -             | 0.16      |

| D              |           | 12.00         |           |

| D1             |           |               |           |

| Е              |           | 12.00         |           |

| E1             |           | 10.00         |           |

| e              |           | 0.80          |           |

| b(w/o plating) | 0.25      | 0.30          | 0.35      |

| L              | 0.45      | 0.60          | 0.75      |

| L1             |           | 1.00REF       |           |

| $\theta_{0}$   | 00        | $3.5^{\circ}$ | 7°        |

#### NOTES:

1.JEDEC OUTLINE:MS-026 BSB

2.DIMENSIONS D1 AND E1 D0 NOT INCLUDE MOLD PROTRUSION.

ALLOWBLE PROTRUSION IS

0.25mm PER SIDE. D1 AND E1 ARE MAXIMUM PLASTIC BODY SIZE DIMENSIONS IMCLUDING MOLD MISMATCH.

3.DIMENSION b DOES NOT INCLUDE DAMBAR PROTRUSION.ALLOWBLE DAMBAR PROTRUSION SHALL NOT CAUSE THE LEAD WIDTH TO EXCEED THE MAXIMUN b DIMNSION BY MORE THAN 0.08mm.

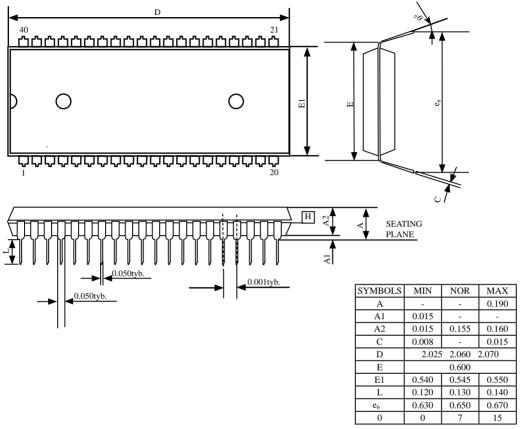

## PDIP-40 OUTLINE PACKAGE

NOTE:

1.JEDEC OUTLINE :MS-011 AC

## PLCC-44 OUTLINE PACKAGE

| l       | DIMEN | SIONS IN | JINCH  | D1141  | LINDICIN | 7 11 1 |

|---------|-------|----------|--------|--------|----------|--------|

| SYMBOLS | DIMEN | SIONS II | N INCH | MI     | LLMETE   | RS     |

|         | MIN   | NOM      | MAX    | MIN    | NOM      | MAX    |

| A       | 0.165 | -        | 0.180  | 4.191  | -        | 4.572  |

| A1      | 0.020 | -        | -      | 0.508  | -        | -      |

| A2      | 0.147 | -        | 0.158  | 3.734  | -        | 4.013  |

| b1      | 0.026 | 0.028    | 0.032  | 0.660  | 0.711    | 0.813  |

| b       | 0.013 | 0.017    | 0.021  | 0.330  | 0.432    | 0.533  |

| С       | 0.007 | 0.010    | 0.0013 | 0.178  | 0.254    | 0.330  |

| D       | 0.650 | 0.653    | 0.656  | 16.510 | 16.586   | 16.662 |

| Е       | 0.650 | 0.653    | 0.656  | 16.510 | 16.586   | 16.662 |

| e       |       | 0.050BSC | ,      |        | 1.270BSC | •      |

| Gd      | 0.590 | 0.610    | 0.630  | 14.986 | 15.494   | 16.002 |

| Ge      | 0.590 | 0.610    | 0.630  | 14.986 | 15.494   | 16.002 |

| Hd      | 0.685 | 0.690    | 0.695  | 17.399 | 17.526   | 17.653 |

0.695

0.112

0.004

17.399

2.540

17.526

17.653

2.845

0.102

0.690

### NOTE:

1.JEDEC OUTLINE: M0-047 AC

2.DATUM PLANE H IS LACATED AT THE BOTTOM OF THE MOLD PARTING LINE COINCIDENT WITH WHERE THE LEAD EXITS THE BODY.

3.DIMENSIONS E AND D D0 NOT INCLUDE MODE PROTRUSION. ALLOWABLE PROTRUSION IS 10 MIL PRE SIDE.DIMENSIONS E AND D D0 INCLUDE MOLD MISMATCH AND ARE DETERMINED AT DATUM PLANE H.

4.DIMENSION 61 DOES NOT INCLUDE DAMBAR PROTRUSION.

STC MCU Limited. 10

0.685

0.100

He

L

Y

# Chapter 2. CLOCK, POWER MANAGENMENT, RESET

#### 2.1 Clock Network

There are two clock sources available for STC11/10Fxx series. One is the clock from crystal oscillation and the other is from internal simple RC oscillation.

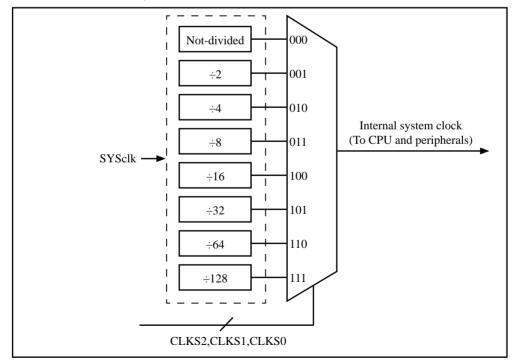

#### CLK\_DIV register (Clock Divider)

LSB

| bit  | В7 | В6 | В5 | B4 | В3 | B2    | B1    | В0    |

|------|----|----|----|----|----|-------|-------|-------|

| name | -  | -  | -  | -  | -  | CLKS2 | CLKS1 | CLKS0 |

## B2-B0 (CLKS2-CLKS0):

000 clock source is not divided (default state)

001 clock source is divided by 2.

010 clock source is divided by 4.

011 clock source is divided by 8.

100 clock source is divided by 16.

101 clock souece is divided by 32.

110 clock source is divided by 64.

111 clock source is divided by 128.

Clock Structure

## 2.2 Power Management

## **PCON** register

LSB

|   | bit  | В7   | В6    | В5   | B4  | В3  | B2  | B1 | В0  |

|---|------|------|-------|------|-----|-----|-----|----|-----|

| n | name | SMOD | SMOD0 | LVDF | POF | GF1 | GF0 | PD | IDL |

SMOD: Double baud rate bit when the UART is used in mode 1,2 or 3.

SMOD0: SM0/FE bit select for SCON.7

LVDF : Low-Voltage Flag. It is set if the voltage is below the LVD reference voltage.

POF : Power-On flag. It is set by power-off-on action and can only cleared by software.

GF1 : General-purposed flag 1

GF0 : General-purposed flag 0

PD : Power-Down bit.

IDL : Idle mode bit.

#### 2.2.1 Idle Mode

An instruction that sets IDL/PCON.0 causes that to be the last instruction executed before going into the idle mode, the internal clock is gated off to the CPU but not to the interrupt, timer, WDT and serial port functions. The CPU status is preserved in its entirety: the Stack Pointer, Program Counter, Program Status Word, Accumulator, and all other registers maintain their data during Idle. The port pins hold the logical states they had at the time Idle was activated. ALE and PSEN hold at logic high levels.

There are two ways to terminate the idle. Activation of any enabled interrupt will cause PCON.0 to be cleared by hardware, terminating the idle mode. The interrupt will be serviced, and following RETI, the next instruction to be executed will be the one following the instruction that put the device into idle.

The flag bits (GFO and GF1) can be used to give art indication if an interrupt occurred during normal operation or during Idle. For example, an instruction that activates Idle can also set one or both flag bits. When Idle is terminated by an interrupt, the interrupt service routine can examine the flag bits.

The other way to wake-up from idle is to pull RESET high to generate internal hardware reset. Since the clock oscillator is still running, the hardware reset needs to be held active for only two system clock cycles (24 system clock) to complete the reset.

#### 2.2.2 Slow Down Mode

A divider is designed to slow down the clock source prior to route to all logic circuit. The operating frequency of internal logic circuit can therefore be slowed down dynamically, and then save the power.

#### 2.2.3 Power Down (PD) Mode

An instruction that sets PCON.1 cause that to be the last instruction executed before going into the PD mode. In the PD mode, the on-chip oscillator is stopped. The contents of on-chip RAM and SFRs are maintained. The power-down mode can be woken-up by RESET pin, external interrupt INTO ~ INT1, RXD pin, T0 pin, T1 pin and PCA input pins-cex0 and cex1. When it is woken-up by RESET, the program will execute from the address 0x0000. Be carefully to keep RESET pin active for at least 10ms in order for a stable clock. If it is woken-up from I/O, the CPU will rework through jumping to related interrupt service routine. Before the CPU rework, the clock is blocked and counted until 32768 in order for denouncing the unstable clock. To use I/O wake-up, interrupt-related registers have to be enabled and programmed accurately before power-down is entered. Pay attention to have at least one "NOP" instruction subsequent to the power-down instruction if I/O wake-up is used.

## 2.3 RESET Control

In STC12C5A60S2, there are 6 sources to generate internal reset. They are RESET (P4.7) pin, Watch-Dog-Timer, software reset, On-chip power-on-reset and On-chip MAX810 POR timing delay.

### 2.3.1 Reset pin

The P4.7 pin, if configured as RESET pin function(default), is input pin for chip reset. A level change of RESET pin have to keep at least 24 cycles plus 10us in order for CPU internal sampling use.

#### 2.3.2 Power-On Reset (POR)

When VCC drops below the detection threshold of POR circuit, all of the logic circuits are reset.

When VCC goes back up again, an internal reset is released automatically after a delay of 32768 clocks. The nominal POR detection threshold is around 1.9V for 3V device and 3.3V for 5V device.

## 2.3.3 Watch-Dog-Timer

An overflow of Watch-Dog-Timer will generate a internal reset.

WDT\_CONTR: Watch-Dog-Timer Control Register

| bit  | B7       | В6 | B5     | B4      | В3       | B2  | B1  | В0  |

|------|----------|----|--------|---------|----------|-----|-----|-----|

| name | WDT_FLAG | -  | EN_WDT | CLR_WDT | IDLE_WDT | PS2 | PS1 | PS0 |

WDT\_FLAG: WDT reset flag.

0: This bit should be cleared by software.

1 : When WDT overflows, this bit is set by hardware to indicate a WDT reset happened.

#### 2.3.4 Software RESET

Writing an "1" to SWRST bit in IAP\_CONTR register will generate a internal reset.

### IAP\_CONTR: ISP/IAP Control Register

| bit  | В7    | В6   | В5    | B4       | В3 | B2  | B1  | В0  |

|------|-------|------|-------|----------|----|-----|-----|-----|

| name | IAPEN | SWBS | SWRST | CMD_FAIL | -  | WT2 | WT1 | WT0 |

IAPEN: ISP/IAP operation enable.

0: Global disable all ISP/IAP program/erase/read function.

1: Enable ISP/IAP program/erase/read function.

SWBS: software boot selection control.

0: Boot from main-memory after reset.

1: Boot from ISP memory after reset.

SWRST: software reset trigger control.

0: No operation

1: Generate software system reset. It will be cleared by hardware automatically.

CMD\_FAIL: Command Fail indication for ISP/IAP operation.

0: The last ISP/IAP command has finished successfully.

1: The last ISP/IAP command fails. It could be caused since the access of flash memory was inhibited.

## 2.3.5 MAX810 power-on-reset delay

There is another on-chip POR delay circuit is integrated on STC11/10Fxx. This circuit is like MAX810 and is controlled by configuring flash Option Register. Very long POR delay time – around 200ms will be generated by this circuit once it is enabled.

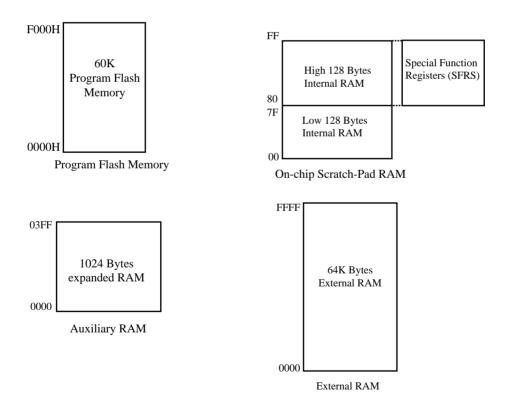

# **Chapter 3. Memory Organization**

## 3.1 Program Flash Memory

There is 60K-bytes of flash memory embedded for program and data storage. The design allows users to configure it as like there are three individual partition banks inside. They are called AP region, IAP region and ISP boot region. AP region is the space that user program is resided. IAP(In-Application-Program) region is the nonvolatile data storage space that may be used to save important parameters by AP program. In other words, the IAP capability of STC11/10Fxx series provide the user to read/write the user-defined on-chip data flash region to save the needing in use of external EEPROM device. ISP boot region is the space that allows a specific program we calls "ISP program" is resided. Inside the ISP region, the user can also enable read/write access to a small memory space to store parameters for specific purposes. This small space is called "ISP data flash" and can be enabled via programming NVM option registers. Generally, the purpose of ISP program is to fulfill AP program upgrade without the need to remove the device from system, STC11/10Fxx series hardware catches the configuration information since power-up duration and performs out-of-space hardware-protection depending on pre-determined criteria. The criteria is AP region can be accessed by ISP program only, IAP region can be accessed by ISP program and AP program, and ISP region is prohibited access from AP program and ISP program itself. But if the "ISP data flash is enabled", ISP program can read/write this space. When wrong settings on ISP-IAP SFRs are done, The "out-of-space" happens and STC11/10Fxx series follow the criteria above, ignore the trigger command.

STC MCU Limited

15

Figure 21, The 2052 Date Mark

## 3.2 Data Memory

## 3.2.1 On-chip Scratch-Pad RAM

Just the same as the conventional 8051 micro-controller, there are 256 bytes of SRAM data memory plus 128 bytes of SFR space available on the STC11/10Fxx series. The lower 128 bytes of data memory may be accessed through both direct and indirect addressing. The upper 128 bytes of data memory and the 128 bytes of SFR space share the same address space. The upper 128 bytes of data memory may only be accessed using indirect addressing. The 128 bytes of SFR can only be accessed through direct addressing. The lower 32 bytes of data memory are grouped into 4 banks of 8 registers each. The RSO and RS1 bits in PSW register select which register bank is in use. Instructions using register addressing will only access the currently specified bank.

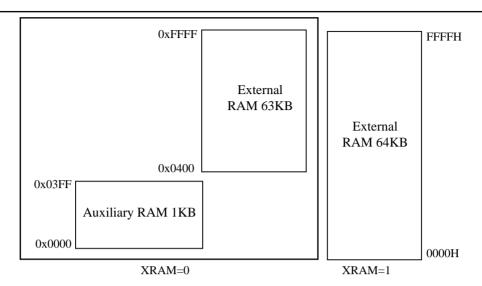

#### 3.2.2 Auxiliary RAM

There are 1024 bytes of additional data RAM available on STC11/10Fxx series. They may be accessed by the instructions MOVX @Ri or MOVX @DPTR. A control bit – XRAM located in AUXR.1 register is to control access of auxiliary RAM. When set, disable the access of auxiliary RAM. When clear (ERAM=0), this auxiliary RAM is the default target for the address range from 0x0000 to 0x03FF. If ERAM=0 and the target address is over 0x03FF, switches to access external RAM automatically. When ERAM=0, the content in DPH is ignored when the instruction MOVX @Ri is executed.

#### 3.2.3 External RAM

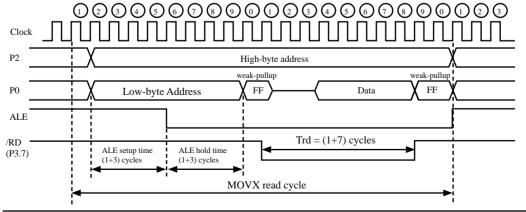

There is 64K-byte addressing space available for STC11/10Fxx series to access external data RAM. Just the same as the design in the conventional 8051, the port – P2, P0, ALE, P3.6 and P3.7 have alterative function for external data RAM access. In addition, a new register BUS\_SPEED (address: 0x8F) is design to stretch the cycle time of MOVX instruction. In BUS\_SPEED register, {ALES1 and ALES0} is to stretch the setup time and hold time with respect to ALE negative edge and {RW2, RW1, RW0} is to stretch the pulse width of /WR(P3.6) and /RD(P3.7). By using BUS\_SPEED to change the instruction cycle time, STC11/10Fxx series can conformed to communicate with both of fast and slow peripheral devices without loss of communication efficiency.

#### 3.2.4 Special Function Register for RAM

For fast data movement, STC11/10Fxx series support two data pointers. They share the same SFR address and are switched by the register bit – DPS.

### **AUXR** register

LSB

| bit  | В7    | В6    | B5        | B4   | В3 | B2     | B1   | В0    |

|------|-------|-------|-----------|------|----|--------|------|-------|

| name | T0x12 | T1x12 | UART_M0x6 | BRTR | -  | BRTx12 | XRAM | S1BRS |

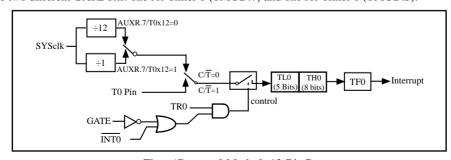

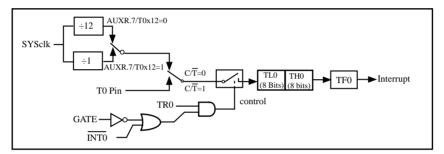

#### T0x12

0: The clock source of Timer 0 is SYSclk/12.

1: The clock source of Timer 0 is SYSclk/1.

#### T1x12

0 : The clock source of Timer 1 is SYSclk/12.

1 : The clock source of Timer 1 is SYSclk/1.

#### UART M0x6

0 : The baud-rate of UART in mode 0 is SYSclk/12.1 : The baud-rate of UART in mode 0 is SYSclk/2.

#### **BRTR**

0 : The baud-rate generator of UART is stopped.1 : The baud-rate generator of UART is enabled.

B3: resevered.

#### BRTx12

0 : The baud-rate generator is incremented every 12 system clocks.

1 : The baud-rate generator is incremented every system clock.

#### XRAM

0 : On-chip auxiliary RAM is enabled and located at the address 0x0000 to 0x03FF. For address over 0x03FF, off-chip external RAM becomes the target automatically.

1 : On-chip auxiliary RAM is always disabled.

#### S1BRS

0 : Timer 1 is used for the baud-rate generator.

1 : Timer 1 is released to use in other functions, and enhanced UART is used for the baud-rate generator.

## **AUXR1** register

LSB

| bit  | В7      | B6 | B5 | B4 | В3  | B2 | B1 | В0  |

|------|---------|----|----|----|-----|----|----|-----|

| name | UART_P1 | -  | -  | -  | GF2 | -  | -  | DPS |

GF2: General Flag. It can be used by software.

DPS: DPTR registers select bit.

0: DPTR0 is selected(Default).

1 : The secondary DPTR(DPTR 1) is switched to use.

### BUS\_SPEED register

LSB

| bit  | В7 | В6 | B5    | B4    | В3 | B2   | B1   | В0   |

|------|----|----|-------|-------|----|------|------|------|

| name | -  | -  | ALES1 | ALES0 | -  | RWS2 | RWS1 | RWS0 |

#### {ALES1 and ALES0}:

00: The P0 address setup time and hold time to ALE negative edge is one clock cycle

01: The P0 address setup time and hold time to ALE negative edge is two clock cycles.

10: The P0 address setup time and hold time to ALE negative edge is three clock cycles. (default)

11: The P0 address setup time and hold time to ALE negative edge is four clock cycles.

#### {RWS2,RWS1,RWS0}:

000: The MOVX read/write pulse is 1 clock cycle.

001: The MOVX read/write pulse is 2 clock cycles.

010: The MOVX read/write pulse is 3 clock cycles.

011: The MOVX read/write pulse is 4 clock cycles. (default)

100: The MOVX read/write pulse is 5 clock cycles.

101: The MOVX read/write pulse is 6 clock cycles.

110: The MOVX read/write pulse is 7 clock cycles.

111: The MOVX read/write pulse is 8 clock cycles.

When the target is on-chip auxiliary RAM, the setting on BUS\_SPEED register is discarded by hardware.

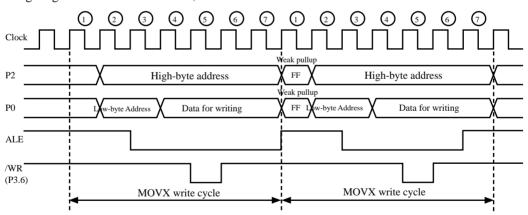

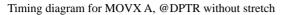

## Timing diagram for MOVX @DPTR, A without stretch

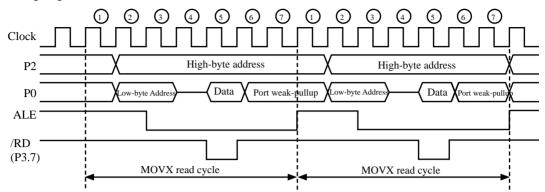

Timing diagram for MOVX @DPTR, A with stretch {RWS2,RWS1,RWS0} = 3'b111 Twr = 8 clock cycles (Twr is stretched by 7 cycles).

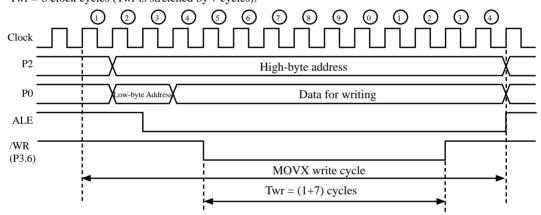

Timing diagram for MOVX @DPTR, A with stretch  $\{RWS2,RWS1,RWS0\} = 3'b111$  and  $\{ALES1,ALES0\} = 2'b11$

The Trd is stretched by 7, so Twr = 8 clock cycles. TALES is stretched by 3, so TALES = 4 clock cycles and TALEH = 4 clock cycles.

# **Chapter 4. Configurable I/O Ports**

## 4.1 I/O Port Configurations

All port pins on STC11/10Fxx series may be independently configured to one of four modes: quasi-bidirectional (standard 8051 port output), push-pull output, input-only or open-drain output. All port pins default to quasi-bidirectional after reset. Each one has a Schmitt-triggered input for improved input noise rejection.

P4.5, and P4.7 are located at the pins-ALE, and RST of conventional 80C51. Pay attention that additional control bits on P4SW register are used to enable the I/O port functions of these pins. Prior to use them as I/O port, the users must set the corresponding bit to enable it.

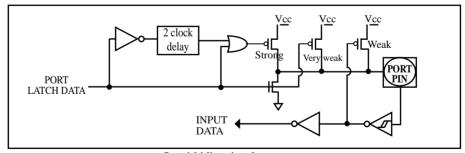

### 4.1.1 Quasi-bidirectional I/O

Port pins in quasi-bidirectional output mode function similar to the standard 8051 port pins. A quasi-bidirectional port can be used as an input and output without the need to reconfigure the port. This is possible because when the port outputs a logic high, it is weakly driven, allowing an external device to pull the pin low. When the pin outputs low, it is driven strongly and able to sink a large current. There are three pull-up transistors in the quasi-bidirectional output that serve different purposes.

One of these pull-ups, called the "very weak" pull-up, is turned on whenever the port register for the pin contains a logic "1". This very weak pull-up sources a very small current that will pull the pin high if it is left floating.

A second pull-up, called the "weak" pull-up, is turned on when the port register for the pin contains a logic "1" and the pin itself is also at a logic "1" level. This pull-up provides the primary source current for a quasi-bidirectional pin that is outputting a 1. If this pin is pulled low by the external device, this weak pull-up turns off, and only the very weak pull-up remains on. In order to pull the pin low under these conditions, the external device has to sink enough current to over-power the weak pull-up and pull the port pin below its input threshold voltage.

The third pull-up is referred to as the "strong" pull-up. This pull-up is used to speed up low-to-high transitions on a quasi-bidirectional port pin when the port register changes from a logic "0" to a logic "1". When this occurs, the strong pull-up turns on for two CPU clocks, quickly pulling the port pin high.

Quasi-bidirectional output

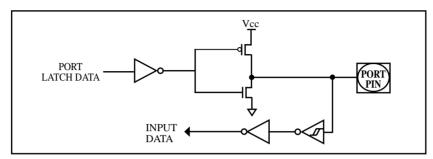

## 4.1.2 Push-pull Output

The push-pull output configuration has the same pull-down structure as both the open-drain and the quasi-bidirectional output modes, but provides a continuous strong pull-up when the port register conatins a logic "1". The push-pull mode may be used when more source current is needed from a port output. In addition, input path of the port pin in this configuration is also the same as quasi-bidirectional mode.

Push-pull output

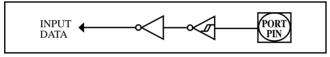

## 4.1.3 Input-only Mode

The input-only configuration is a Schmitt-triggered input without any pull-up resistors on the pin.

Input-only Mode

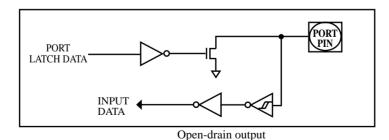

## 4.1.4 Open-drain Output

The open-drain output configuration turns off all pull-ups and only drives the pull-down transistor of the port pin when the port register contains a logic "0". To use this configuration in application, a port pin must have an external pull-up, typically tied to VCC. The input path of the port pin in this configuration is the same as quasi-bidirection mode.

STC MCU Limited. 22

# 4.2 I/O Port Registers

All port pins on STC11/10Fxx series may be independently configured by software to one of four types on a bit-by-bit basis, as shown in next Table. Two mode registers for each port select the output mode for each port pin.

Table: Configuration of I/O port mode.

| PxM1.n | PxM0.n | Port Mode                   |  |  |  |

|--------|--------|-----------------------------|--|--|--|

| 0      | 0      | Quasi-bidirectional         |  |  |  |

| 0      | 1      | Push-Pull output            |  |  |  |

| 1      | 0      | Input Only (High-impedance) |  |  |  |

| 1      | 1      | Open-Drain Output           |  |  |  |

## P0M0 register

| bit  | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|------|--------|--------|--------|--------|--------|--------|--------|--------|

| name | P0M0.7 | P0M0.6 | P0M0.5 | P0M0.4 | P0M0.3 | P0M0.2 | P0M0.1 | P0M0.0 |

## P0M1 register

| bit  | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|------|--------|--------|--------|--------|--------|--------|--------|--------|

| name | P0M1.7 | P0M1.6 | P0M1.5 | P0M1.4 | P0M1.3 | P0M1.2 | P0M1.1 | P0M1.0 |

## P1M0 register

|   | bit  | 7            | 6 | 5      | 4      | 3      | 2      | 1      | 0      |

|---|------|--------------|---|--------|--------|--------|--------|--------|--------|

| ſ | name | P1M0.7 P1M0. |   | P1M0.5 | P1M0.4 | P1M0.3 | P1M0.2 | P1M0.1 | P1M0.0 |

## P1M1 register

| bit  | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|------|--------|--------|--------|--------|--------|--------|--------|--------|

| name | P1M1.7 | P1M1.6 | P1M1.5 | P1M1.4 | P1M1.3 | P1M1.2 | P1M1.1 | P1M1.0 |

## P2M0 register

| bit  | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|------|--------|--------|--------|--------|--------|--------|--------|--------|

| name | P2M0.7 | P2M0.6 | P2M0.5 | P2M0.4 | P2M0.3 | P2M0.2 | P2M0.1 | P2M0.0 |

## P2M1 register

| bit  | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|------|--------|--------|--------|--------|--------|--------|--------|--------|

| name | P2M1.7 | P2M1.6 | P2M1.5 | P2M1.4 | P2M1.3 | P2M1.2 | P2M1.1 | P2M1.0 |

## P3M0 register

| bit  | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|------|--------|--------|--------|--------|--------|--------|--------|--------|

| name | P3M0.7 | P3M0.6 | P3M0.5 | P3M0.4 | P3M0.3 | P3M0.2 | P3M0.1 | P3M0.0 |

## P3M1 register

| bit  | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|------|--------|--------|--------|--------|--------|--------|--------|--------|

| name | P3M1.7 | P3M1.6 | P3M1.5 | P3M1.4 | P3M1.3 | P3M1.2 | P3M1.1 | P3M1.0 |

## P4M0 register

| bit  | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|------|--------|--------|--------|--------|--------|--------|--------|--------|

| name | P4M0.7 | P4M0.6 | P4M0.5 | P4M0.4 | P4M0.3 | P4M0.2 | P4M0.1 | P4M0.0 |

## P4M1 register

| bit  | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|------|--------|--------|--------|--------|--------|--------|--------|--------|

| name | P4M1.7 | P4M1.6 | P4M1.5 | P4M1.4 | P4M1.3 | P4M1.2 | P4M1.1 | P4M1.0 |

## P4SW register

| bit  | D7 | D6      | D5       | D4      | D3 | D2 | D1 | D0 |

|------|----|---------|----------|---------|----|----|----|----|

| name | -  | NA_P4.6 | ALE_P4.5 | NA_P4.4 | -  | -  | -  | -  |

NA\_P4.6: Set this bit to enable P4.6. (Pin Location: Convention 80C51's EA).

0: the pin is always kept at weak-high state.

1: the pin functions as P4.6.

ALE\_P4.5 : Set this bit to switch ALE to become P4.5. (Pin Location : Convention 80C51's ALE)

0: the pin functions as ALE output for use in MOVX instruction only.

1: the pin functions as P4.5.

NA\_P4.4: Set this bit to enable P4.4. (Pin Location: Convention 80C51's PSEN)

0: the pin is always kept at weak-high state.

1: the pin functions as P4.4

# **Chapter 5 Instruction System**

# **5.1 Special Function Registers**

|      | 0/8       | 1/9       | 2/A       | 3/B       | 4/C       | 5/D       | 6/E       | 7/F       |       |

|------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-------|

| 0F8H |           |           |           |           |           |           |           |           | 0FFH  |

|      |           |           |           |           |           |           |           |           |       |

| 0F0H | В         |           |           |           |           |           |           |           | 0F7H  |

|      | 0000,0000 |           |           |           |           |           |           |           |       |

| 0E8H |           |           |           |           |           |           |           |           | 0EFH  |

| 0E0H | ACC       |           |           |           |           |           |           |           | 0E7H  |

| OEOH | 0000,0000 |           |           |           |           |           |           |           | UE/H  |

| 0D8H | 0000,0000 |           |           |           |           |           |           |           | 0DFH  |

| 0D0H | PSW       |           |           |           |           |           |           |           | 0D7H  |

| obon | 0000,0000 |           |           |           |           |           |           |           | OD/II |

| 0C8H |           |           |           |           |           |           |           |           | 0CFH  |

| 0C0H | P4        | WDT_CONR  | IAP_DATA  | IAP_ADDRH | IAP_ADDRL | IAP_CMD   | IAP_TRIG  | IAP_CONTR | 0C7H  |

|      | 1111,1111 | xx00,0000 | 1111,1111 | 0000,0000 | 0000,0000 | xxxx,xx00 | xxxx,xxxx | 0000,0000 |       |

| 0B8H | IP        | SADEN     |           | P4SW      |           |           |           |           | 0BFH  |

|      | x0x0,0000 | 0000,0000 |           | x000,xxxx |           |           |           |           |       |

| 0B0H | Р3        | P3M1      | P3M0      | P4M1      | P4M0      |           |           |           | 0B7H  |

|      | 1111,1111 | 0000,0000 | 0000,0000 | 0000,0000 | 0000,0000 |           |           |           |       |

| 0A8H | ΙE        | SADDR     | WKTCL     | WKTCH     |           |           |           |           | 0AFH  |

|      | 00x0,0000 | 0000,0000 | 0000,0000 | 0xxx,0000 |           |           |           |           |       |

| 0A0H | P2        | BUS_SPEED | AUXR1     |           |           |           |           | Don't use | 0A7H  |

|      | 1111,1111 | xx10,x011 | xxxx,0xx0 |           |           |           |           |           |       |

| 098H | SCON      | SBUF      |           |           | BRT       |           |           |           | 09FH  |

|      | 0000,0000 | xxxx,xxxx |           |           | 0000,0000 |           |           |           |       |

| 090H | P1        | P1M1      | P1M0      | P0M1      | P0M0      | P2M1      | P2M0      | CLK_DIV   | 097H  |

|      | 1111,1111 | 0000,0000 | 0000,0000 | 0000,0000 | 0000,0000 | 0000,0000 | 0000,0000 | xxxx,x000 |       |

| 088H | TCON      | TMOD      | TL0       | TL1       | TH0       | TH1       | AUXR      | WAKE_CLKO | 08FH  |

|      | 0000,0000 | 0000,0000 | 0000,0000 | 0000,0000 | 0000,0000 | 0000,0000 | 0000,x000 | x000,x000 |       |

| 080H | P0        | SP        | DPL       | DPH       |           |           |           | PCON      | 087H  |

|      | 1111,1111 | 0000,0111 | 0000,0000 | 0000,0000 |           |           |           | 0011,0000 |       |

|      | 0/8       | 1/9       | 2/A       | 3/B       | 4/C       | 5/D       | 6/E       | 7/F       |       |

| Symbol    | Description                                    | Address | Bit Address and Symbol MSB LSB                                                           | Value after<br>Power-on or<br>Reset |

|-----------|------------------------------------------------|---------|------------------------------------------------------------------------------------------|-------------------------------------|

| P0        | Port 0                                         | 80H     | P0.7   P0.6   P0.5   P0.4   P0.3   P0.2   P0.1   P0.0                                    | 1111 1111B                          |

| SP        | Stack Pointer                                  | 81H     |                                                                                          | 0000 0111B                          |

| DPL DPL   | Data Pointer Low                               | 82H     |                                                                                          | 0000 0000B                          |

| DPTR DPH  | Data Pointer High                              | 83H     |                                                                                          | 0000 0000B                          |

| PCON      | Power Control                                  | 87H     | SMOD SMODO LVDF POF GF1 GF0 PD IDL                                                       | 0011 0000B                          |

| TCON      | Timer Control                                  | 88H     | TF1 TR1 TF0 TR0 IE1 IT1 IE0 IT0                                                          | 0000 0000B                          |

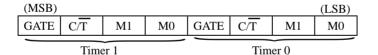

| TMOD      | Timer Mode                                     | 89H     | GATE $\mid C/\overline{T} \mid M1 \mid M0 \mid GATE \mid C/\overline{T} \mid M1 \mid M0$ | 0000 0000B                          |

| TL0       | Timer Low 0                                    | 8AH     |                                                                                          | 0000 0000B                          |

| TL1       | Timer Low 1                                    | 8BH     |                                                                                          | 0000 0000B                          |

| TH0       | Timer High 0                                   | 8CH     |                                                                                          | 0000 0000B                          |

| TH1       | Timer High 1                                   | 8DH     |                                                                                          | 0000 0000B                          |

| AUXR      | Auxiliary register                             | 8EH     | T0x12 T1x12 UART_M0x6 BRTR - BRTx12 XRAM S1BRS                                           | 0000 0000B                          |

| WAKE_CLKO | CLK_Output Power down Wake-up control register | 8FH     | - RXD_PIN_IE T1_PIN_IE T0_PIN_IE - BRTCLKO T1CLKO T0CLKO                                 | 0000 0000B                          |

| P1        | Port 1                                         | 90H     | P1.7   P1.6   P1.5   P1.4   P1.3   P1.2   P1.1   P1.0                                    | 1111 1111B                          |

| P1M1      | P1 configuration 1                             | 91H     |                                                                                          | 0000 0000B                          |

| P1M0      | P1 configuration 0                             | 92H     |                                                                                          | 0000 0000B                          |

| P0M1      | P0 configuration 1                             | 93H     |                                                                                          | 0000 0000B                          |

| P0M0      | P0 configuration 0                             | 94H     |                                                                                          | 0000 0000B                          |

| P2M1      | P2 configuration 1                             | 95H     |                                                                                          | 0000 0000B                          |

| P2M0      | P2 configuration 0                             | 96H     |                                                                                          | 0000 0000B                          |

| CLK_DIV   | Clock Divder                                   | 97h     | -   -   -   -   CLKS2   CLKS1   CLKS0                                                    | xxxx x000B                          |

| SCON      | Serial Control                                 | 98H     | SM0/FE SM1 SM2 REN TB8 RB8 TI RI                                                         | 0000 0000B                          |

| SBUF      | Serial Buffer                                  | 99H     |                                                                                          | xxxx xxxxB                          |

| BRT       | dedicated Baud-<br>Rate Timer                  | 9СН     |                                                                                          | 0000 0000B                          |

| P2        | Port 2                                         | A0H     | P2.7   P2.6   P2.5   P2.4   P2.3   P2.2   P2.1   P2.0                                    | 1111 1111B                          |

| BUS_SPEED | Bus-Speed Control                              | A1H     | -   -   ALES1   ALES0   -   RWS2   RWS1   RWS0                                           | xx10 x011B                          |

| AUXR1     | Auxiliary register1                            | A2H     | UART_P1 GF2 DPS                                                                          | 0xxx 0xx0B                          |

| IE        | Interrupt Enable                               | A8H     | EA ELVD - ES ETI EXI ETO EXO                                                             | 0x00 0000B                          |

| SADDR     | Slave Address                                  | А9Н     |                                                                                          | 0000 0000B                          |

| P3        | Port 3                                         | ВОН     | P3.7   P3.6   P3.5   P3.4   P3.3   P3.2   P3.1   P3.0                                    | 1111 1111B                          |

| P3M1      | P3 configuration 1                             | B1H     |                                                                                          | 0000 0000B                          |

| Symbol    | Description                         | Address | Bit Address and Symbol MSB LSB                        | Value after<br>Power-on or<br>Reset |

|-----------|-------------------------------------|---------|-------------------------------------------------------|-------------------------------------|

| P3M0      | P3 configuration 0                  | B2H     |                                                       | 0000 0000B                          |

| P4M1      | P4 configuration 1                  | ВЗН     |                                                       | 0000 0000B                          |

| P4M0      | P4 configuration 0                  | B4H     |                                                       | 0000 0000B                          |

| IP        | Interrupt Priority<br>Low           | В8Н     | - PLVD PADC PS PT1 PX1 PT0 PX0                        | 0000 0000B                          |

| SADEN     | Slave Address Mask                  | В9Н     |                                                       | 0000 0000B                          |

| P4SW      | Port 4 switch                       | ВВН     | - NA_P4.6 ALE_P4.5 NA_P4.4                            | x000 xxxxB                          |

| P4        | Port 4                              | C0H     | P4.7   P4.6   P4.5   P4.4   P4.3   P4.2   P4.1   P4.0 | 1111 1111B                          |

| WDT_CONTR | Watch-Dog-Timer<br>Control Register | C1H     | WDT_FLAG - EN_WDT CLR_WDT IDLE_WDT PS2 PS1 PS0        | xx00 0000B                          |

| IAP_DATA  | ISP/IAP Flash Data<br>Register      | С2Н     |                                                       | 1111 1111B                          |

| IAP_ADDRH | ISP/IAP Flash<br>Address High       | СЗН     |                                                       | 0000 0000В                          |

| IAP_ADDRL | ISP/IAP Flash<br>Address Low        | С4Н     |                                                       | 0000 0000B                          |

| IAP_CMD   | ISP/IAP Flash<br>Command Register   | С5Н     | MS1 MS0                                               | xxxx x000B                          |

| IAP_TRIG  | ISP/IAP Flash<br>Command Trigger    | С6Н     |                                                       | xxxx xxxxB                          |

| IAP_CONTR | ISP/IAP Control<br>Register         | С7Н     | IAPEN SWBS SWRST CMD_FAIL - WT2 WT1 WT0               | 0000 x000B                          |

| PSW       | Program Status<br>Word              | D0H     | CY AC F0 RS1 RS0 OV F1 P                              | 0000 0000B                          |

| В         | B Register                          | F0H     |                                                       | 0000 0000B                          |

#### Accumulator

ACC is the Accumulator register. The mnemonics for accumulator-specific instructions, however, refer to the accumulator simply as A.

## **B-Register**

The B register is used during multiply and divide operations. For other instructions it can be treated as another scratch pad register.

## **Stack Pointer**

The Stack Pointer register is 8 bits wide. It is incremented before data is stored during PUSH and CALL executions. While the stack may reside anywhee in on-chip RAM, the Stack Pointer is initialized to 07H after a reset. This causes the stack to begin at location 08H.

## Program Status Word(PSW)

The program status word(PSW) contains several status bits that reflect the current state of the CPU. The PSW, shown below, resides in the SFR space. It contains the Carry bit, the Auxiliary Carry(for BCD operation), the two register bank select bits, the Overflow flag, a Parity bit and two user-definable status flags.

The Carry bit, other than serving the function of a Carry bit in arithmetic operations, also serves as the "Accumulator" for a number of Boolean operations.

The bits RS0 and RS1 are used to select one of the four register banks shown in the previous page. A number of instructions refer to these RAM locations as R0 through R7.

The Parity bit reflects the number of 1s in the Accumulator. P=1 if the Accumulator contains an odd number of 1s and otherwise P=0.

#### **PSW** register

| bit  | 7  | 6  | 5  | 4   | 3   | 2  | 1  | 0 |

|------|----|----|----|-----|-----|----|----|---|

| name | CY | AC | F0 | RS1 | RS0 | OV | F1 | P |

CY: Carry flag.

AC: Auxilliary Carry Flag.(For BCD operations)

F0: Flag 0.(Available to the user for general purposes)

RS1: Register bank select control bit 1. RS0: Register bank select control bit 0.

OV: Overflow flag.

F1: Flag 1. User-defined flag.

P : Parity flag.

#### **Data Pointer**

The Data Pointer (DPTR) consists of a high byte (DPH) and a low byte (DPL). Its intended function is to hold a 16-bit address. It may be manipulated as a 16-bit register or as two independent 8-bit registers.

## 5.2 Addressing Modes

#### Direct Addressing(DIR)

In direct addressing the operand is specified by an 8-bit address field in the instruction. Only internal data RAM and SFRs can be direct addressed.

#### Indirect Addressing(IND)

In indirect addressing the instruction specified a register which contains the address of the operand. Both internal and external RAM can be indirectly addressed.

The address register for 8-bit addresses can be R0 or R1 of the selected bank, or the Stack Pointer.

The address register for 16-bit addresses can only be the 16-bit data pointer register – DPTR.

## Register Instruction(REG)

The register banks, containing registers R0 through R7, can be accessed by certain instructions which carry a 3-bit register specification within the opcode of the instruction. Instructions that access the registers this way are code efficient because this mode eliminates the need of an extra address byte. When such instruction is executed, one of the eight registers in the selected bank is accessed.

#### **Register-Specific Instruction**

Some instructions are specific to a certain register. For example, some instructions always operate on the accumulator or data pointer, etc. No address byte is needed for such instructions. The opcode itself does it.

## Immediate Constant(IMM)

The value of a constant can follow the opcode in the program memory.

#### **Index Addressing**

Only program memory can be accessed with indexed addressing and it can only be read. This addressing mode is intended for reading look-up tables in program memory. A 16-bit base register(either DPTR or PC) points to the base of the table, and the accumulator is set up with the table entry number. Another type of indexed addressing is used in the conditional jump instruction.

In conditional jump, the destination address is computed as the sum of the base pointer and the accumulator.

# **5.3 Instruction Set Summary**

| Mnemonic |           | Description                                   |   | Execution cycles of conventional 8051 | Execution cycles of STC11F60XE |

|----------|-----------|-----------------------------------------------|---|---------------------------------------|--------------------------------|

| ARITH    | METIC (   | OPERATIONS                                    |   |                                       |                                |

| ADD      | A, Rn     | Add register to Accumulator                   | 1 | 12                                    | 2                              |

| ADD      | A, direct | Add ditect byte to Accumulator                | 2 | 12                                    | 3                              |

| ADD      | A, @Ri    | Add indirect RAM to Accumulator               | 1 | 12                                    | 3                              |

| ADD      | A, #data  | Add immediate data to Accumulator             | 2 | 12                                    | 2                              |

| ADDC     | A, Rn     | Add register to Accumulator with Carry        | 1 | 12                                    | 2                              |

| ADDC     | A, direct | Add direct byte to Accumulator with Carry     | 2 | 12                                    | 3                              |

| ADDC     | A, @Ri    | Add indirect RAM to Accumulator with Carry    | 1 | 12                                    | 3                              |

| ADDC     | A, #data  | Add immediate data to Acc with Carry          | 2 | 12                                    | 2                              |

| SUBB     | A, Rn     | Subtract Register from Acc wih borrow         | 1 | 12                                    | 2                              |

| SUBB     | A, direct | Subtract direct byte from Acc with borrow     | 2 | 12                                    | 3                              |

| SUBB     | A, @Ri    | Subtract indirect RAM from ACC with borrow    | 1 | 12                                    | 3                              |

| SUBB     | A, #data  | Substract immediate data from ACC with borrow | 2 | 12                                    | 2                              |

| INC      | A         | Increment Accumulator                         | 1 | 12                                    | 2                              |

| INC      | Rn        | Increment register                            | 1 | 12                                    | 3                              |

| INC      | direct    | Increment direct byte                         | 2 | 12                                    | 4                              |

| INC      | @Ri       | Increment direct RAM                          | 1 | 12                                    | 4                              |

| DEC      | A         | Decrement Accumulator                         | 1 | 12                                    | 2                              |

| DEC      | Rn        | Decrement Register                            | 1 | 12                                    | 3                              |

| DEC      | direct    | Decrement direct byte                         | 2 | 12                                    | 4                              |

| DEC      | @Ri       | Decrement indirect RAM                        | 1 | 12                                    | 4                              |

| INC      | DPTR      | Increment Data Pointer                        | 1 | 24                                    | 1                              |

| MUL      | AB        | Multiply A & B                                | 1 | 48                                    | 4                              |

| DIV      | AB        | Divde A by B                                  | 1 | 48                                    | 5                              |

| DA       | A         | Decimal Adjust Accumulator                    | 1 | 12                                    | 4                              |

| N     | Mnemonic     | Description                                | Byte | Execution cycles of conventional 8051 | Execution cycles of STC11F60XE |

|-------|--------------|--------------------------------------------|------|---------------------------------------|--------------------------------|

| LOGIC | AL OPERATIO  | ONS                                        |      |                                       |                                |

| ANL   | A, Rn        | AND Register to Accumulator                | 1    | 12                                    | 2                              |

| ANL   | A, direct    | AND direct btye to Accumulator             | 2    | 12                                    | 3                              |

| ANL   | A, @Ri       | AND indirect RAM to Accumulator            | 1    | 12                                    | 3                              |

| ANL   | A, #data     | AND immediate data to Accumulator          | 2    | 12                                    | 2                              |

| ANL   | direct, A    | AND Accumulator to direct byte             | 2    | 12                                    | 4                              |

| ANL   | direct,#data | AND immediate data to direct byte          | 3    | 24                                    | 4                              |

| ORL   | A, Rn        | OR register to Accumulator                 | 1    | 12                                    | 2                              |

| ORL   | A,direct     | OR direct byte to Accumulator              | 2    | 12                                    | 3                              |

| ORL   | A,@Ri        | OR indirect RAM to Accumulator             | 1    | 12                                    | 3                              |

| ORL   | A, #data     | OR immediate data to Accumulator           | 2    | 12                                    | 2                              |

| ORL   | direct, A    | OR Accumulator to direct byte              | 2    | 12                                    | 4                              |

| ORL   | direct,#data | OR immediate data to direct byte           | 3    | 24                                    | 4                              |

| XRL   | A, Rn        | Exclusive-OR register to Accumulator       | 1    | 12                                    | 2                              |

| XRL   | A, direct    | Exclusive-OR direct byte to Accumulator    | 2    | 12                                    | 3                              |

| XRL   | A, @Ri       | Exclusive-OR indirect RAM to Accumulator   | 1    | 12                                    | 3                              |

| XRL   | A, #data     | Exclusive-OR immediate data to Accumulator | 2    | 12                                    | 2                              |

| XRL   | direct, A    | Exclusive-OR Accumulator to direct byte    | 2    | 12                                    | 4                              |

| XRL   | direct,#data | Exclusive-OR immediate data to direct byte | 3    | 24                                    | 4                              |

| CLR   | A            | Clear Accumulator                          | 1    | 12                                    | 1                              |

| CPL   | A            | Complement Accumulator                     | 1    | 12                                    | 2                              |

| RL    | A            | Rotate Accumulator Left                    | 1    | 12                                    | 1                              |

| RLC   | A            | Rotate Accumulator Left through the Carry  | 1    | 12                                    | 1                              |

| RR    | A            | Rotate Accumulator Right                   | 1    | 12                                    | 1                              |

| RRC   | A            | Rotate Accumulator Right through the Carry | 1    | 12                                    | 1                              |

| SWAP  | A            | Swap nibbles within the Accumulator        | 1    | 12                                    | 1                              |

| N      | Inemonic      | Description                                    | Byte | Execution cycles of conventional 8051 | Execution cycles of STC11F60XE |

|--------|---------------|------------------------------------------------|------|---------------------------------------|--------------------------------|

| DATA 7 | TRANSFER      |                                                |      |                                       |                                |

| MOV    | A, Rn         | Move register to Accumulator                   | 1    | 12                                    | 1                              |

| MOV    | A, direct     | Move direct byte to Accumulator                | 2    | 12                                    | 2                              |

| MOV    | A,@Ri         | Move indirect RAM to                           | 1    | 12                                    | 2                              |

| MOV    | A, #data      | Move immediate data to Accumulator             | 2    | 12                                    | 2                              |

| MOV    | Rn, A         | Move Accumulator to register                   | 1    | 12                                    | 2                              |

| MOV    | Rn, direct    | Move direct byte to register                   | 2    | 24                                    | 4                              |

| MOV    | Rn, #data     | Move immediate data to register                | 2    | 12                                    | 2                              |

| MOV    | direct, A     | Move Accumulator to direct byte                | 2    | 12                                    | 3                              |

| MOV    | direct, Rn    | Move register to direct byte                   | 2    | 24                                    | 3                              |

| MOV    | direct,direct | Move direct byte to direct                     | 3    | 24                                    | 4                              |

| MOV    | direct, @Ri   | Move indirect RAM to direct byte               | 2    | 24                                    | 4                              |

| MOV    | direct,#data  | Move immediate data to direct byte             | 3    | 24                                    | 3                              |

| MOV    | @Ri, A        | Move Accumulator to indirect RAM               | 1    | 12                                    | 3                              |

| MOV    | @Ri, direct   | Move direct byte to indirect RAM               | 2    | 24                                    | 4                              |

| MOV    | @Ri, #data    | Move immediate data to indirect RAM            | 2    | 12                                    | 3                              |

| MOV    | DPTR,#data16  | Move immdiate data to indirect RAM             | 2    | 12                                    | 3                              |

| MOVC   | A,@A+DPTR     | Move Code byte relative to DPTR to Acc         | 1    | 24                                    | 4                              |

| MOVC   | A, @A+PC      | Move Code byte relative to PC to Acc           | 1    | 24                                    | 4                              |

| MOVX   | A,@Ri         | Move External RAM(16-bit addr) to Acc          | 1    | 24                                    | 4                              |

| MOVX   | A,@DPTR       | Move External RAM(16-bit addr) to Acc          | 1    | 24                                    | 3                              |

| MOVX   | @Ri, A        | Move Acc to External RAM(8-bit addr)           | 1    | 24                                    | 3                              |

| MOVX   | @DPTR,A       | Move Acc to External RAM (16-bit addr)         | 1    | 24                                    | 3                              |

| PUSH   | direct        | Push direct byte onto stack                    | 2    | 24                                    | 4                              |

| POP    | direct        | POP direct byte from stack                     | 2    | 24                                    | 3                              |

| XCH    | A,Rn          | Exchange register with Accumulator             | 1    | 12                                    | 3                              |

| XCH    | A, direct     | Exchange direct byte with Accumulator          | 2    | 12                                    | 4                              |

| XCH    | A, @Ri        | Exchange indirect RAM with Accumulator         | 1    | 12                                    | 4                              |

| XCHD   | A, @Ri        | Exchange low-order Digit indirect RAM with Acc | 1    | 12                                    | 4                              |

| M      | Inemonic      | Description                                         | Byte | Execution cycles of conventional 8051 | Execution cycles of STC11F60XE |

|--------|---------------|-----------------------------------------------------|------|---------------------------------------|--------------------------------|

| BOOLE  | AN VARIABLE   | MANIPULATION                                        |      |                                       |                                |

| CLR    | C             | Clear Carry                                         | 1    | 12                                    | 1                              |

| CLR    | bit           | Clear direct bit                                    | 2    | 12                                    | 4                              |

| SETB   | C             | Set Carry                                           | 1    | 12                                    | 1                              |

| SETB   | bit           | Set direct bit                                      | 2    | 12                                    | 4                              |

| CPL    | C             | Complement Carry                                    | 1    | 12                                    | 1                              |

| CPL    | bit           | Complement direct bit                               | 2    | 12                                    | 4                              |

| ANL    | C, bit        | AND direct bit to Carry                             | 2    | 24                                    | 3                              |

| ANL    | C, /bit       | AND complement of direct bit to Carry               | 2    | 24                                    | 3                              |

| ORL    | C, bit        | OR direct bit to Carry                              | 2    | 24                                    | 3                              |

| ORL    | C, /bit       | OR complement of direct bit to Carry                | 2    | 24                                    | 3                              |

| MOV    | C, bit        | Move direct bit to Carry                            | 2    | 12                                    | 3                              |

| MOV    | bit, C        | Move Carry to direct bit                            | 2    | 24                                    | 4                              |

| JC     | rel           | Jump if Carry is set                                | 2    | 24                                    | 3                              |

| JNC    | rel           | Jump if Carry not set                               | 2    | 24                                    | 3                              |

| JB     | bit, rel      | Jump if direct bit is set                           | 3    | 24                                    | 4                              |

| JNB    | bit,rel       | Jump if direct bit is not set                       | 3    | 24                                    | 4                              |

| JBC    | bit, rel      | Jump if direct bit is set & clear bit               | 3    | 24                                    | 5                              |

| PROGR. | AM BRANCHI    | NG                                                  |      |                                       |                                |

| ACALL  | addr11        | Absolute Subroutine Call                            | 2    | 24                                    | 6                              |

| LCALL  | addr16        | Long Subroutine Call                                | 3    | 24                                    | 6                              |

| RET    |               | Return from Subroutine                              | 1    | 24                                    | 4                              |

| RETI   |               | Return from interrupt                               | 1    | 24                                    | 4                              |

| AJMP   | addr11        | Absolute Jump                                       | 2    | 24                                    | 3                              |

| LJMP   | addr16        | Long Jump                                           | 3    | 24                                    | 4                              |

| SJMP   | rel           | Short Jump (relative addr)                          | 2    | 24                                    | 3                              |

| JMP    | @A+DPTR       | Jump indirect relative to the DPTR                  | 1    | 24                                    | 3                              |

| JZ     | rel           | Jump if Accumulator is Zero                         | 2    | 24                                    | 3                              |

| JNZ    | rel           | Jump if Accumulator is not Zero                     | 2    | 24                                    | 3                              |

| CJNE   | A,direct,rel  | Compare direct byte to Acc and jump if not equal    | 3    | 24                                    | 5                              |

| CJNE   | A,#data,rel   | Compare immediate to Acc and Jump if not equal      | 3    | 24                                    | 4                              |

| CJNE   | Rn,#data,rel  | Compare immediate to register and Jump if not equal | 3    | 24                                    | 4                              |

| CJNE   | @Ri,#data,rel | Compare immediate to indirect and jump if not equal | 3    | 24                                    | 5                              |

| DJNZ   | Rn, rel       | Decrement register and jump if not Zero             | 2    | 24                                    | 4                              |

| DJNZ   | direct, rel   | Decrement direct byte and Jump if not Zero          |      | 24                                    | 5                              |

| NOP    |               | No Operation                                        | 1    | 12                                    | 1                              |

# Chapter 6. Interrupt

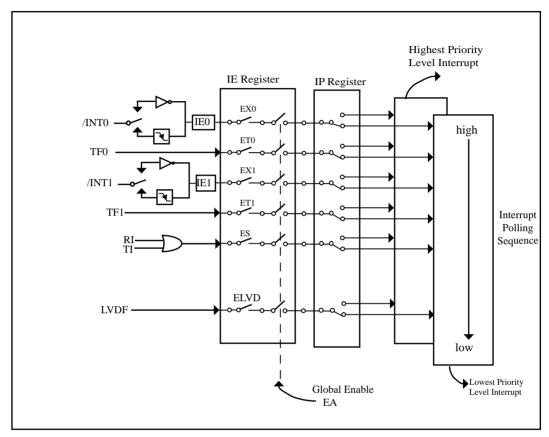

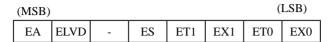

There are 6 interrupt vector addresses available in STC11/10Fxx series. Associating with each interrupt vector, the interrupt sources can be individually enabled or disabled by setting or clearing a bit in the registers IE. The register also contains a global disable bit(EA), which can be cleared to disable all interrupts at once.

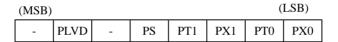

Each interrupt source has two corresponding bits to represent its priority. Higher-priority interrupt will be not interrupted by lower-priority interrupt request. If two interrupt requests of different priority levels are received simultaneously, the request of higher priority is serviced. If interrupt requests of the same priority level are received simultaneously, an internal polling sequence determine which request is serviced. The following table shows the internal polling sequence in the same priority level and the interrupt vector address.

| Interrupt Source                | Vector<br>address | C          | Interrupt Priority setting( IP) | Priority 0<br>(lowest) | Priority<br>1 | Interrupt<br>Request | Interrupt<br>Enable<br>Control Bit |

|---------------------------------|-------------------|------------|---------------------------------|------------------------|---------------|----------------------|------------------------------------|