# STC12C2052AD series MCU STC12LE2052AD series MCU Data Sheet

STC MCU Limited

Update date: 2011-7-15

# **CONTENTS**

| Chapter 1. Introduction                                                        | 7    |

|--------------------------------------------------------------------------------|------|

| 1.1 Features                                                                   | 7    |

| 1.2 Block diagram                                                              |      |

| 1.3 Pin Configurations                                                         |      |

| 1.4 STC12C2052AD series Selection Table                                        |      |

| 1.5 STC12C2052AD series Minimum Application System                             |      |

| 1.6 STC12C2052AD series MCU Typical Application Circuit for ISP                |      |

| 1.7 Pin Descriptions                                                           |      |

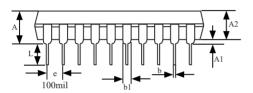

| 1.8 Package Dimension Drawings                                                 |      |

|                                                                                |      |

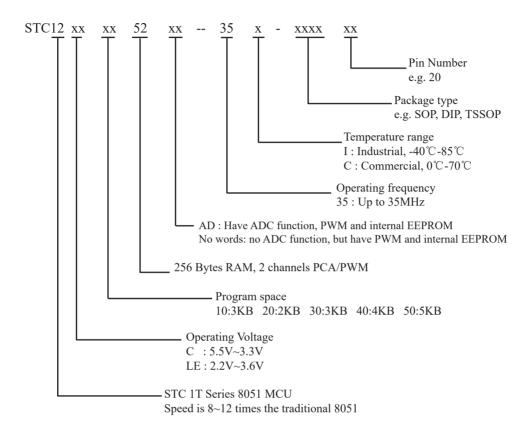

| 1.9 STC12C2052AD series MCU naming rules                                       | 10   |

|                                                                                |      |

| Chapter 2. Clock, Power Management and Reset                                   |      |

| 2.1 Clock                                                                      |      |

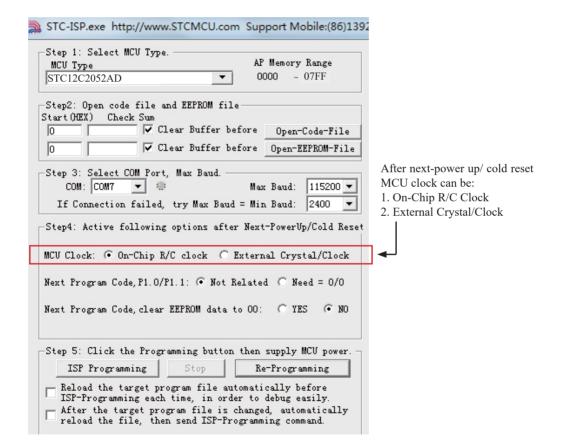

| 2.1.1 On-Chip R/C Clock and External Crystal/Clcok are Optional in STC-ISP.exe | 22   |

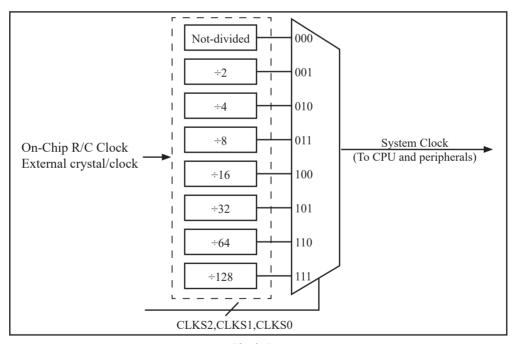

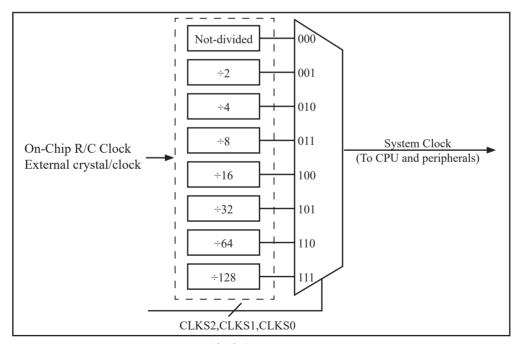

| 2.1.2 Divider for System Clock                                                 |      |

| 2.1.3 How to Know Internal RC Oscillator frequency(Internal clock frequency)   |      |

| 2.1.4 Programmable Clock Output                                                |      |

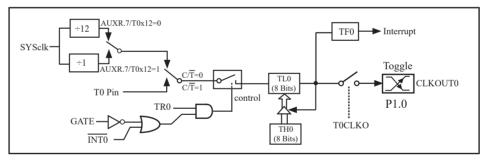

| 2.1.4.1 Timer 0 Programmable Clock-out on P1.0                                 |      |

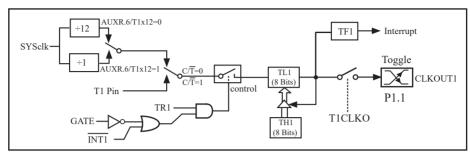

| 2.1.4.2 Timer 1 Programmable Clock-out on P1.1                                 |      |

| 2.2 Power Management Modes                                                     |      |

| 2.2.1 Slow Down Mode                                                           |      |

| 2.2.2 Idle Mode                                                                |      |

| 2.2.3 Stop / Power Down (PD) Mode and Demo Program (C and ASM)                 |      |

| 2.3 RESET Sources                                                              |      |

| 2.3.1 RESET Pin                                                                |      |

| 2.3.2 Software RESET                                                           |      |

| 2.3.3 Power-On Reset (POR)                                                     |      |

| 2.3.4 MAX810 power-on-Reset delay                                              |      |

| 2.3.5 Internal Low Voltage Detection Reset                                     |      |

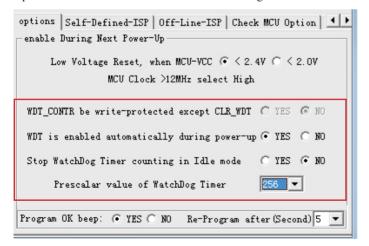

| 2.3.6 Watch-Dog-Timer                                                          |      |

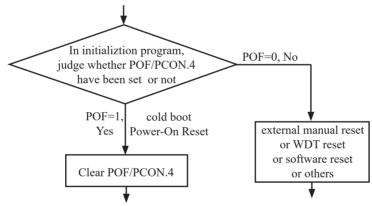

| 2.3.7 Warm Boot and Cold Boot Reset                                            | . 48 |

| 3.1 Program Memory       49         3.2 Data Memory(SRAM)       50         3.3 Special Function Registers       53         3.3.1 Special Function Registers Bits Description       54         Chapter 4. Configurable I/O Ports of STC12C2052AD series58         4.1 I/O Ports Configurations       58         4.2 I/O ports Modes       60         4.2.1 Quasi-bidirectional I/O       60         4.2.2 Push-pull Output       61         4.2.3 Input-only (High-Impedance) Mode       61         4.2.4 Open-drain Output       61         4.3 I/O port application notes       62         4.4 Typical transistor control circuit       62         4.5 Typical diode control circuit       62         4.6 3V/5V hybrid system       63         4.7 How to make I/O port low after MCU reset       64         4.8 I/O status while PWM outputing       64         4.9 I/O drive LED application circuit       65         4.10 I/O immediately drive LCD application circuit       66         4.11 Using A/D Conversion to scan key application circuit       66         4.11 Using A/D Conversion to scan key application circuit       67         Chapter 5. Instruction System       68         5.1 Addressing Modes       68         5.2 Instruction Definitions                                      | Chapter 3. Memory Organization                    | 49        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|-----------|

| 3.2 Data Memory(SRAM)       50         3.3 Special Function Registers       53         3.3.1 Special Function Registers Address Map       53         3.3.2 Special Function Registers Bits Description       54         Chapter 4. Configurable I/O Ports of STC12C2052AD series 58         4.1 I/O Ports Configurations       58         4.2 I/O ports Modes       60         4.2.1 Quasi-bidirectional I/O       60         4.2.2 Push-pull Output       61         4.2.3 Input-only (High-Impedance) Mode       61         4.2.4 Open-drain Output       61         4.3 I/O port application notes       62         4.4 Typical transistor control circuit       62         4.5 Typical diode control circuit       62         4.6 3V/5V hybrid system       63         4.7 How to make I/O port low after MCU reset       64         4.8 I/O status while PWM outputing       64         4.9 I/O drive LED application circuit       65         4.10 I/O immediately drive LCD application circuit       66         4.11 Using A/D Conversion to scan key application circuit       67         Chapter 5. Instruction System       68         5.1 Addressing Modes       68         5.2 Instruction Definitions       74         Chapter 6. Interrupt System <th>3.1 Program Memory</th> <th>49</th> | 3.1 Program Memory                                | 49        |

| 3.3 Special Function Registers       53         3.3.1 Special Function Registers Address Map       53         3.3.2 Special Function Registers Bits Description       54         Chapter 4. Configurable I/O Ports of STC12C2052AD series 58         4.1 I/O Ports Configurations       58         4.2 I/O ports Modes       60         4.2.1 Quasi-bidirectional I/O       60         4.2.2 Push-pull Output       61         4.2.3 Input-only (High-Impedance) Mode       61         4.2.4 Open-drain Output       61         4.3 I/O port application notes       62         4.4 Typical transistor control circuit       62         4.5 Typical diode control circuit       62         4.5 Typical diode control circuit       62         4.6 3V/5V hybrid system       63         4.7 How to make I/O port low after MCU reset       64         4.8 I/O status while PWM outputing       64         4.9 I/O drive LED application circuit       65         4.10 I/O immediately drive LCD application circuit       66         4.11 Using A/D Conversion to scan key application circuit       67         Chapter 5. Instruction System       68         5.1 Addressing Modes       68         5.2 Instruction Definitions       74         Chapter 6. Interru                                      |                                                   |           |

| 3.3.2 Special Function Registers Bits Description       54         Chapter 4. Configurable I/O Ports of STC12C2052AD series 58       4.1 I/O Ports Configurations       58         4.2 I/O ports Modes       60         4.2.1 Quasi-bidirectional I/O       60         4.2.2 Push-pull Output       61         4.2.3 Input-only (High-Impedance) Mode       61         4.2.4 Open-drain Output       61         4.3 I/O port application notes       62         4.4 Typical transistor control circuit       62         4.5 Typical diode control circuit       62         4.5 Typical diode control circuit       62         4.6 3V/5V hybrid system       63         4.7 How to make I/O port low after MCU reset       64         4.8 I/O status while PWM outputing       64         4.9 I/O drive LED application circuit       65         4.10 I/O immediately drive LCD application circuit       66         4.11 Using A/D Conversion to scan key application circuit       67         Chapter 5. Instruction System       68         5.1 Addressing Modes       68         5.2 Instruction Definitions       74         Chapter 6. Interrupt System       111         6.1 Interrupt Register       115         6.3 Interrupt Priorities       125                                               |                                                   |           |

| Chapter 4. Configurable I/O Ports of STC12C2052AD series 58         4.1 I/O Ports Configurations       58         4.2 I/O ports Modes       60         4.2.1 Quasi-bidirectional I/O       60         4.2.2 Push-pull Output       61         4.2.3 Input-only (High-Impedance) Mode       61         4.2.4 Open-drain Output       61         4.3 I/O port application notes       62         4.4 Typical transistor control circuit       62         4.5 Typical diode control circuit       62         4.5 Typical diode control circuit       62         4.6 3V/5V hybrid system       63         4.7 How to make I/O port low after MCU reset       64         4.8 I/O status while PWM outputing       64         4.9 I/O drive LED application circuit       65         4.10 I/O immediately drive LCD application circuit       66         4.11 Using A/D Conversion to scan key application circuit       67         Chapter 5. Instruction System       68         5.1 Addressing Modes       68         5.2 Instruction Definitions       74         Chapter 6. Interrupt System       111         6.1 Interrupt Register       113         6.2 Interrupt Priorities       125         6.3 How Interrupts Are Handled       126                                                               | 3.3.1 Special Function Registers Address Map      | 53        |

| 4.1 I/O Ports Configurations       58         4.2 I/O ports Modes       60         4.2.1 Quasi-bidirectional I/O       60         4.2.2 Push-pull Output       61         4.2.3 Input-only (High-Impedance) Mode       61         4.2.4 Open-drain Output       61         4.3 I/O port application notes       62         4.4 Typical transistor control circuit       62         4.5 Typical diode control circuit       62         4.5 Typical diode control circuit       62         4.6 3V/5V hybrid system       63         4.7 How to make I/O port low after MCU reset       64         4.8 I/O status while PWM outputing       64         4.9 I/O drive LED application circuit       65         4.10 I/O immediately drive LCD application circuit       66         4.11 Using A/D Conversion to scan key application circuit       67         Chapter 5. Instruction System       68         5.1 Addressing Modes       68         5.2 Instruction Definitions       74         Chapter 6. Interrupt System       111         6.1 Interrupt Register       115         6.3 Interrupt Priorities       125         6.4 How Interrupts Are Handled       126         6.5 External Interrupts       127 <td></td> <td></td>                                                                     |                                                   |           |

| 4.2 I/O ports Modes       60         4.2.1 Quasi-bidirectional I/O       60         4.2.2 Push-pull Output       61         4.2.3 Input-only (High-Impedance) Mode       61         4.2.4 Open-drain Output       61         4.3 I/O port application notes       62         4.4 Typical transistor control circuit       62         4.5 Typical diode control circuit       62         4.5 Typical diode control circuit       62         4.6 3V/5V hybrid system       63         4.7 How to make I/O port low after MCU reset       64         4.8 I/O status while PWM outputing       64         4.9 I/O drive LED application circuit       65         4.10 I/O immediately drive LCD application circuit       66         4.11 Using A/D Conversion to scan key application circuit       67         Chapter 5. Instruction System       68         5.1 Addressing Modes       68         5.2 Instruction Set Summary       69         5.3 Instruction Definitions       74         Chapter 6. Interrupt System       111         6.1 Interrupt Register       115         6.3 Interrupt Priorities       125         6.4 How Interrupts Are Handled       126         6.5 External Interrupts       127 <th>Chapter 4. Configurable I/O Ports of STC12C2052AD</th> <th>series 58</th>            | Chapter 4. Configurable I/O Ports of STC12C2052AD | series 58 |

| 4.2.1 Quasi-bidirectional I/O       60         4.2.2 Push-pull Output       61         4.2.3 Input-only (High-Impedance) Mode       61         4.2.4 Open-drain Output       61         4.3 I/O port application notes       62         4.4 Typical transistor control circuit       62         4.5 Typical diode control circuit       62         4.6 3V/5V hybrid system       63         4.7 How to make I/O port low after MCU reset       64         4.8 I/O status while PWM outputing       64         4.9 I/O drive LED application circuit       65         4.10 I/O immediately drive LCD application circuit       66         4.11 Using A/D Conversion to scan key application circuit       67         Chapter 5. Instruction System       68         5.1 Addressing Modes       68         5.2 Instruction Set Summary       69         5.3 Instruction Definitions       74         Chapter 6. Interrupt System       111         6.1 Interrupt Register       113         6.2 Interrupt Priorities       125         6.4 How Interrupts Are Handled       126         6.5 External Interrupts       127                                                                                                                                                                                  | 4.1 I/O Ports Configurations                      | 58        |

| 4.4 Typical transistor control circuit       62         4.5 Typical diode control circuit       62         4.6 3V/5V hybrid system       63         4.7 How to make I/O port low after MCU reset       64         4.8 I/O status while PWM outputing       64         4.9 I/O drive LED application circuit       65         4.10 I/O immediately drive LCD application circuit       66         4.11 Using A/D Conversion to scan key application circuit       67         Chapter 5. Instruction System       68         5.1 Addressing Modes       68         5.2 Instruction Set Summary       69         5.3 Instruction Definitions       74         Chapter 6. Interrupt System       111         6.1 Interrupt Register       113         6.2 Interrupt Register       115         6.3 Interrupt Priorities       125         6.4 How Interrupts Are Handled       126         6.5 External Interrupts       127                                                                                                                                                                                                                                                                                                                                                                                 | 4.2 I/O ports Modes                               | 60        |

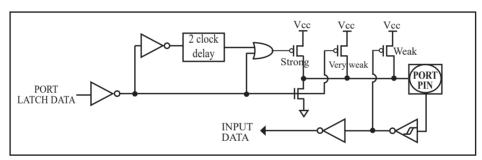

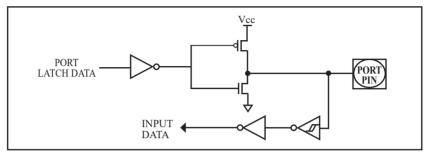

| 4.4 Typical transistor control circuit       62         4.5 Typical diode control circuit       62         4.6 3V/5V hybrid system       63         4.7 How to make I/O port low after MCU reset       64         4.8 I/O status while PWM outputing       64         4.9 I/O drive LED application circuit       65         4.10 I/O immediately drive LCD application circuit       66         4.11 Using A/D Conversion to scan key application circuit       67         Chapter 5. Instruction System       68         5.1 Addressing Modes       68         5.2 Instruction Set Summary       69         5.3 Instruction Definitions       74         Chapter 6. Interrupt System       111         6.1 Interrupt Register       113         6.2 Interrupt Register       115         6.3 Interrupt Priorities       125         6.4 How Interrupts Are Handled       126         6.5 External Interrupts       127                                                                                                                                                                                                                                                                                                                                                                                 | 4.2.1 Quasi-bidirectional I/O                     | 60        |

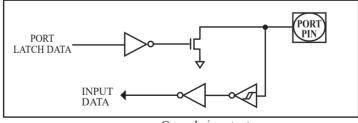

| 4.4 Typical transistor control circuit       62         4.5 Typical diode control circuit       62         4.6 3V/5V hybrid system       63         4.7 How to make I/O port low after MCU reset       64         4.8 I/O status while PWM outputing       64         4.9 I/O drive LED application circuit       65         4.10 I/O immediately drive LCD application circuit       66         4.11 Using A/D Conversion to scan key application circuit       67         Chapter 5. Instruction System       68         5.1 Addressing Modes       68         5.2 Instruction Set Summary       69         5.3 Instruction Definitions       74         Chapter 6. Interrupt System       111         6.1 Interrupt Register       113         6.2 Interrupt Register       115         6.3 Interrupt Priorities       125         6.4 How Interrupts Are Handled       126         6.5 External Interrupts       127                                                                                                                                                                                                                                                                                                                                                                                 | 4.2.2 Push-pull Output                            | 61        |

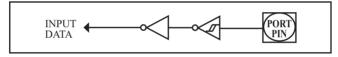

| 4.4 Typical transistor control circuit       62         4.5 Typical diode control circuit       62         4.6 3V/5V hybrid system       63         4.7 How to make I/O port low after MCU reset       64         4.8 I/O status while PWM outputing       64         4.9 I/O drive LED application circuit       65         4.10 I/O immediately drive LCD application circuit       66         4.11 Using A/D Conversion to scan key application circuit       67         Chapter 5. Instruction System       68         5.1 Addressing Modes       68         5.2 Instruction Set Summary       69         5.3 Instruction Definitions       74         Chapter 6. Interrupt System       111         6.1 Interrupt Register       113         6.2 Interrupt Register       115         6.3 Interrupt Priorities       125         6.4 How Interrupts Are Handled       126         6.5 External Interrupts       127                                                                                                                                                                                                                                                                                                                                                                                 | 4.2.3 Input-only (High-Impedance) Mode            | 61        |

| 4.4 Typical transistor control circuit       62         4.5 Typical diode control circuit       62         4.6 3V/5V hybrid system       63         4.7 How to make I/O port low after MCU reset       64         4.8 I/O status while PWM outputing       64         4.9 I/O drive LED application circuit       65         4.10 I/O immediately drive LCD application circuit       66         4.11 Using A/D Conversion to scan key application circuit       67         Chapter 5. Instruction System       68         5.1 Addressing Modes       68         5.2 Instruction Set Summary       69         5.3 Instruction Definitions       74         Chapter 6. Interrupt System       111         6.1 Interrupt Register       113         6.2 Interrupt Register       115         6.3 Interrupt Priorities       125         6.4 How Interrupts Are Handled       126         6.5 External Interrupts       127                                                                                                                                                                                                                                                                                                                                                                                 | 4.2.4 Open-drain Output                           |           |

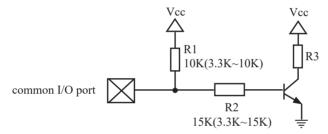

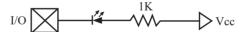

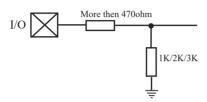

| 4.5 Typical diode control circuit       62         4.6 3V/5V hybrid system       63         4.7 How to make I/O port low after MCU reset       64         4.8 I/O status while PWM outputing       64         4.9 I/O drive LED application circuit       65         4.10 I/O immediately drive LCD application circuit       66         4.11 Using A/D Conversion to scan key application circuit       67         Chapter 5. Instruction System       68         5.1 Addressing Modes       68         5.2 Instruction Set Summary       69         5.3 Instruction Definitions       74         Chapter 6. Interrupt System       111         6.1 Interrupt Register       113         6.2 Interrupt Register       115         6.3 Interrupt Priorities       125         6.4 How Interrupts Are Handled       126         6.5 External Interrupts       127                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4.3 I/O port application notes                    | 02        |

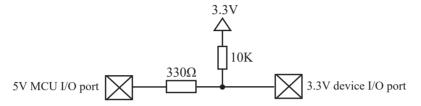

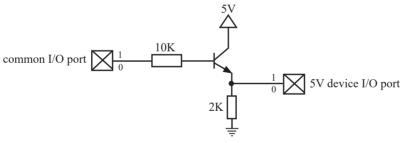

| 4.6       3V/5V hybrid system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                   |           |

| 4.7 How to make I/O port low after MCU reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                   |           |

| 4.8 I/O status while PWM outputing644.9 I/O drive LED application circuit654.10 I/O immediately drive LCD application circuit664.11 Using A/D Conversion to scan key application circuit67Chapter 5. Instruction System685.1 Addressing Modes685.2 Instruction Set Summary695.3 Instruction Definitions74Chapter 6. Interrupt System1116.1 Interrupt Register1136.2 Interrupt Register1156.3 Interrupt Priorities1256.4 How Interrupts Are Handled1266.5 External Interrupts127                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 7 7                                               |           |

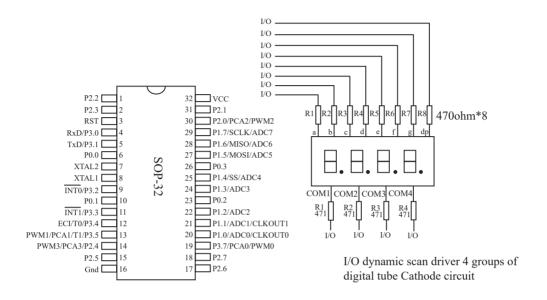

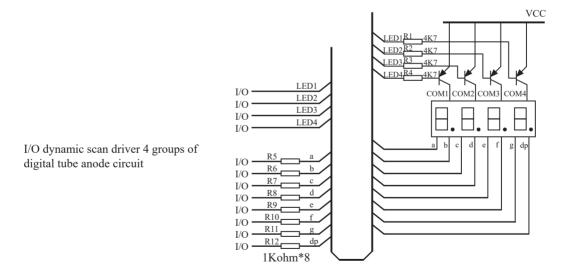

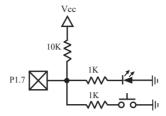

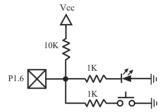

| 4.9 I/O drive LED application circuit654.10 I/O immediately drive LCD application circuit664.11 Using A/D Conversion to scan key application circuit67Chapter 5. Instruction System685.1 Addressing Modes685.2 Instruction Set Summary695.3 Instruction Definitions74Chapter 6. Interrupt System1116.1 Interrupt Structure1136.2 Interrupt Register1156.3 Interrupt Priorities1256.4 How Interrupts Are Handled1266.5 External Interrupts127                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . I f                                             |           |

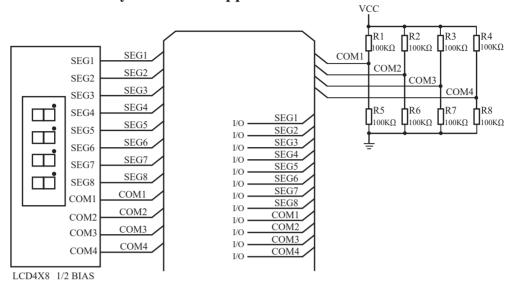

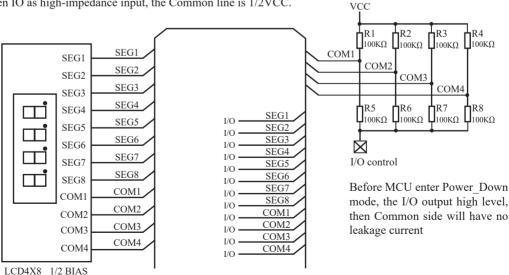

| 4.10 I/O immediately drive LCD application circuit.664.11 Using A/D Conversion to scan key application circuit.67Chapter 5. Instruction System685.1 Addressing Modes685.2 Instruction Set Summary695.3 Instruction Definitions74Chapter 6. Interrupt System1116.1 Interrupt Structure1136.2 Interrupt Register1156.3 Interrupt Priorities1256.4 How Interrupts Are Handled1266.5 External Interrupts127                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                   |           |

| 4.11 Using A/D Conversion to scan key application circuit.67Chapter 5. Instruction System685.1 Addressing Modes685.2 Instruction Set Summary695.3 Instruction Definitions74Chapter 6. Interrupt System1116.1 Interrupt Structure1136.2 Interrupt Register1156.3 Interrupt Priorities1256.4 How Interrupts Are Handled1266.5 External Interrupts127                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | **                                                |           |

| Chapter 5. Instruction System685.1 Addressing Modes685.2 Instruction Set Summary695.3 Instruction Definitions74Chapter 6. Interrupt System1116.1 Interrupt Structure1136.2 Interrupt Register1156.3 Interrupt Priorities1256.4 How Interrupts Are Handled1266.5 External Interrupts127                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | * **                                              |           |

| 5.1 Addressing Modes685.2 Instruction Set Summary695.3 Instruction Definitions74Chapter 6. Interrupt System1116.1 Interrupt Structure1136.2 Interrupt Register1156.3 Interrupt Priorities1256.4 How Interrupts Are Handled1266.5 External Interrupts127                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | · · · · · · · · · · · · · · · · · · ·             |           |

| 5.2 Instruction Set Summary695.3 Instruction Definitions74Chapter 6. Interrupt System1116.1 Interrupt Structure1136.2 Interrupt Register1156.3 Interrupt Priorities1256.4 How Interrupts Are Handled1266.5 External Interrupts127                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -                                                 |           |

| 5.3 Instruction Definitions74Chapter 6. Interrupt System1116.1 Interrupt Structure1136.2 Interrupt Register1156.3 Interrupt Priorities1256.4 How Interrupts Are Handled1266.5 External Interrupts127                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                   |           |

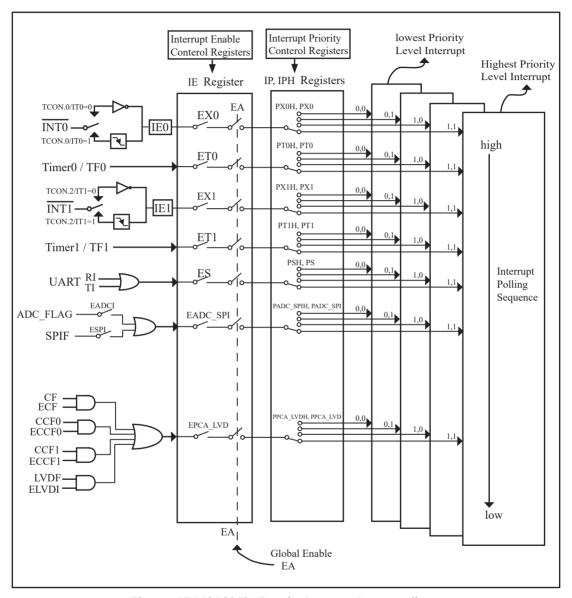

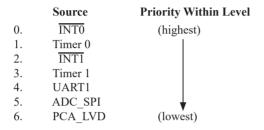

| Chapter 6. Interrupt System1116.1 Interrupt Structure1136.2 Interrupt Register1156.3 Interrupt Priorities1256.4 How Interrupts Are Handled1266.5 External Interrupts127                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ·                                                 |           |

| 6.1 Interrupt Structure1136.2 Interrupt Register1156.3 Interrupt Priorities1256.4 How Interrupts Are Handled1266.5 External Interrupts127                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                   |           |

| 6.2 Interrupt Register1156.3 Interrupt Priorities1256.4 How Interrupts Are Handled1266.5 External Interrupts127                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | • •                                               |           |

| 6.3 Interrupt Priorities1256.4 How Interrupts Are Handled1266.5 External Interrupts127                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1                                                 |           |

| 6.4 How Interrupts Are Handled1266.5 External Interrupts127                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | · ·                                               |           |

| 6.5 External Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                   |           |

| <u>-</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                   |           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6.6 Response Time                                 |           |

| 6.7.1 External Interrupt 0 (INTO) Demo Programs (C and ASM)                                                                                                                                                                                                                                                      | . 132                                                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| 6.7.1 External Interrupt 0 (IN10) Demo Programs (C and ASM)                                                                                                                                                                                                                                                      | 132                                                   |

| 6.7.2 External Interrupt 1 (INT1) Demo Programs (C and ASM)                                                                                                                                                                                                                                                      | 136                                                   |

| 6.7.3 Programs of P3.4/T0 Interrupt(falling edge) used to wake up PD mode                                                                                                                                                                                                                                        |                                                       |

| 6.7.4 Programs of P3.5/T1 Interrupt(falling edge) used to wake up PD mode                                                                                                                                                                                                                                        | 142                                                   |

| 6.7.5 Program of P3.0/RxD Interrupt(falling edge) used to wake up PD mode                                                                                                                                                                                                                                        |                                                       |

| 6.7.6 Program of PCA Interrupt used to wake up Power Down mode                                                                                                                                                                                                                                                   | 147                                                   |

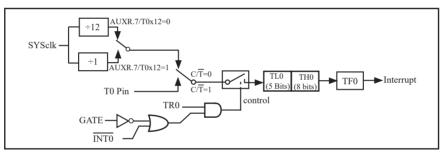

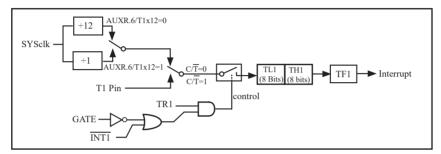

| Chapter 7. Timer/Counter 0/1                                                                                                                                                                                                                                                                                     | .151                                                  |

| 7.1 Special Function Registers about Timer/Counter                                                                                                                                                                                                                                                               | . 151                                                 |

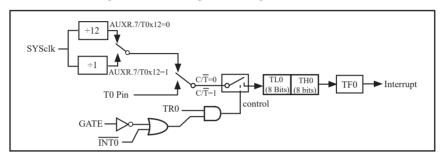

| 7.2 Timer/Counter 0 Mode of Operation (Compatible with traditional 8051 MCU)                                                                                                                                                                                                                                     | 155                                                   |

| 7.2.1 Mode 0 (13-bit Timer/Counter)                                                                                                                                                                                                                                                                              | 155                                                   |

| 7.2.2 Mode 1 (16-bit Timer/Counter) and Demo Programs (C and ASM)                                                                                                                                                                                                                                                | 156                                                   |

| 7.2.3 Mode 2 (8-bit Auto-Reload Mode) and Demo Programs (C and ASM)                                                                                                                                                                                                                                              |                                                       |

| 7.2.4 Mode 3 (Two 8-bit Timers/Couters)                                                                                                                                                                                                                                                                          | 163                                                   |

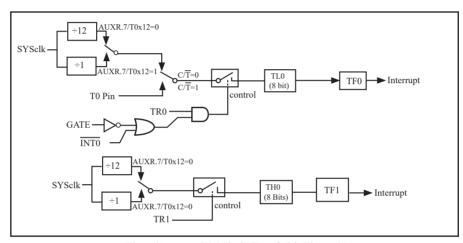

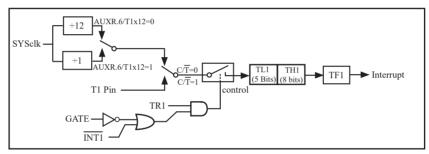

| 7.3 Timer/Counter 1 Mode of Operation                                                                                                                                                                                                                                                                            | . 164                                                 |

| 7.3.1 Mode 0 (13-bit Timer/Counter)                                                                                                                                                                                                                                                                              |                                                       |

| 7.3.2 Mode 1 (16-bit Timer/Counter) and Demo Programs (C and ASM)                                                                                                                                                                                                                                                | 165                                                   |

| 7.3.3 Mode 2 (8-bit Auto-Reload Mode) and Demo Programs (C and ASM)                                                                                                                                                                                                                                              | 169                                                   |

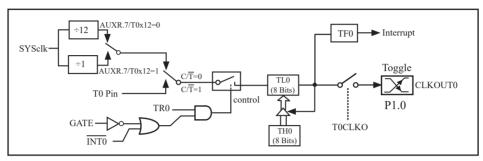

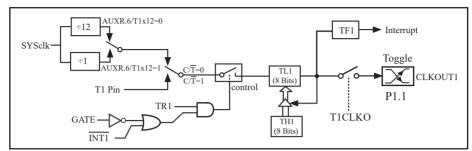

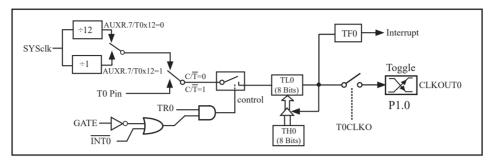

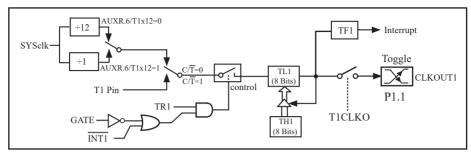

| 7.4 Programmable Clock Output and Demo Programs (C and ASM)                                                                                                                                                                                                                                                      | . 172                                                 |

| 7.4.1 Timer 0 Programmable Clock-out on P1.0 and Demo Program(C and ASM                                                                                                                                                                                                                                          | ).174                                                 |

| 7.4.2 Timer 1 Programmable Clock-out on P1.1 and Demo Program(C and ASM                                                                                                                                                                                                                                          |                                                       |

| 7.5 Application note for Timer in practice                                                                                                                                                                                                                                                                       | . 180                                                 |

| Chapter 8. UART with Enhanced Function                                                                                                                                                                                                                                                                           | .181                                                  |

|                                                                                                                                                                                                                                                                                                                  |                                                       |

| 8.1 Special Function Registers about UART                                                                                                                                                                                                                                                                        | . 181                                                 |

| 8.1 Special Function Registers about UART                                                                                                                                                                                                                                                                        |                                                       |

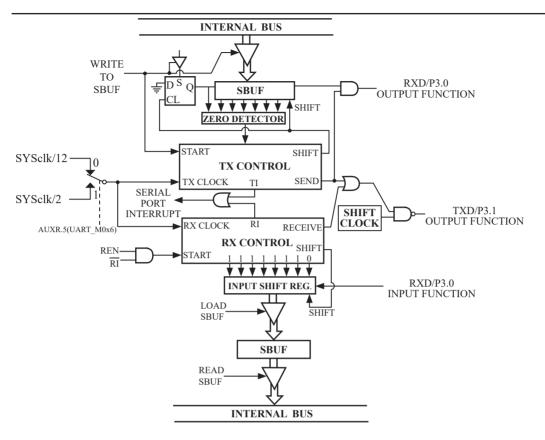

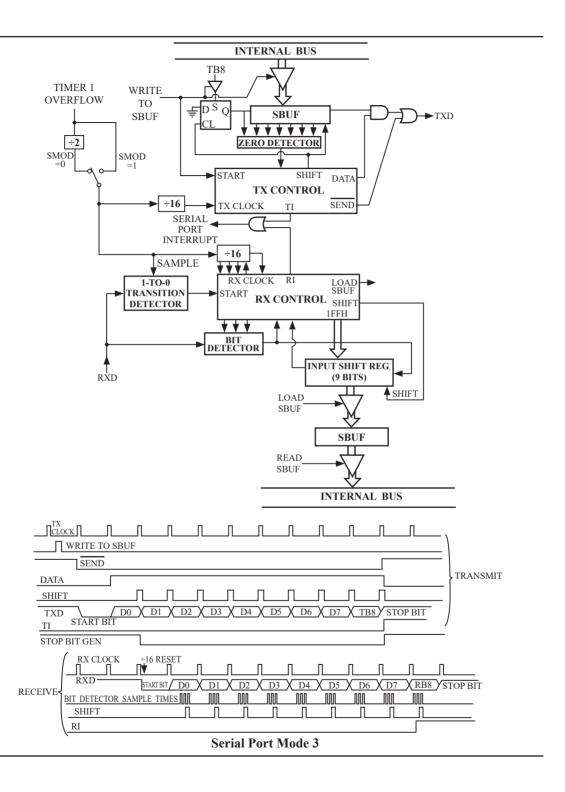

| 8.2 UART Operation Modes                                                                                                                                                                                                                                                                                         | . 185                                                 |

|                                                                                                                                                                                                                                                                                                                  | . 185<br>185                                          |

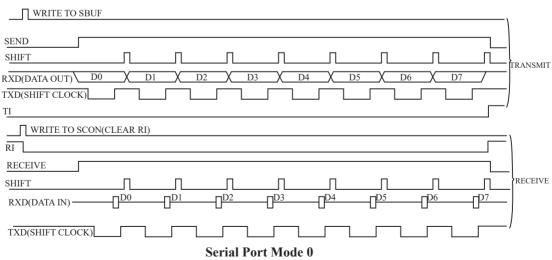

| 8.2 UART Operation Modes                                                                                                                                                                                                                                                                                         | . 185<br>185<br>187                                   |

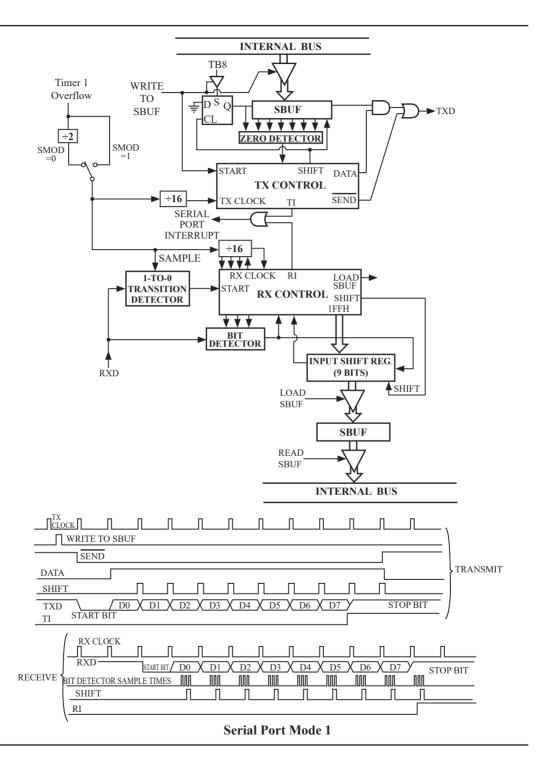

| 8.2 UART Operation Modes                                                                                                                                                                                                                                                                                         | . 185<br>185<br>187<br>189                            |

| 8.2 UART Operation Modes                                                                                                                                                                                                                                                                                         | . 185<br>185<br>187<br>189<br>191                     |

| 8.2 UART Operation Modes  8.2.1 Mode 0: 8-Bit Shift Register                                                                                                                                                                                                                                                     | . 185<br>185<br>187<br>189<br>191<br>. 193            |

| 8.2 UART Operation Modes  8.2.1 Mode 0: 8-Bit Shift Register.  8.2.2 Mode 1: 8-Bit UART with Variable Baud Rate.  8.2.3 Mode 2: 9-Bit UART with Fixed Baud Rate.  8.2.4 Mode 3: 9-Bit UART with Variable Baud Rate.  8.3 Frame Error Detection.  8.4 Multiprocessor Communications                               | . 185<br>185<br>187<br>189<br>191<br>. 193<br>. 193   |

| 8.2 UART Operation Modes  8.2.1 Mode 0: 8-Bit Shift Register  8.2.2 Mode 1: 8-Bit UART with Variable Baud Rate  8.2.3 Mode 2: 9-Bit UART with Fixed Baud Rate  8.2.4 Mode 3: 9-Bit UART with Variable Baud Rate  8.3 Frame Error Detection  8.4 Multiprocessor Communications  8.5 Automatic Address Recognition | . 185<br>187<br>189<br>191<br>. 193<br>. 194          |

| 8.2 UART Operation Modes  8.2.1 Mode 0: 8-Bit Shift Register.  8.2.2 Mode 1: 8-Bit UART with Variable Baud Rate.  8.2.3 Mode 2: 9-Bit UART with Fixed Baud Rate.  8.2.4 Mode 3: 9-Bit UART with Variable Baud Rate.  8.3 Frame Error Detection.  8.4 Multiprocessor Communications                               | . 185<br>187<br>189<br>191<br>. 193<br>. 194<br>. 196 |

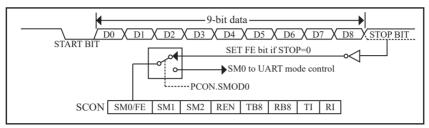

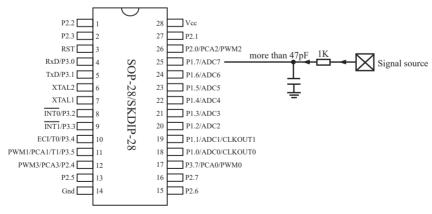

| Chapter 9. Analog to Digital Converter                           | .203  |

|------------------------------------------------------------------|-------|

| 9.1 A/D Converter Structure                                      | . 203 |

| 9.2 Registers for ADC                                            | . 205 |

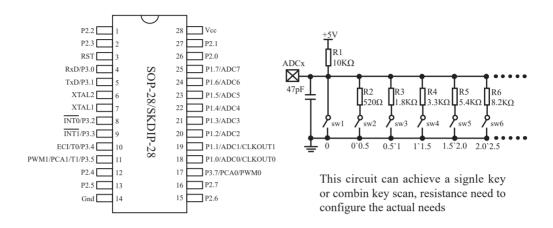

| 9.3 Application Circuit of A/D Converter                         |       |

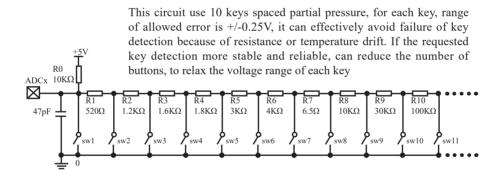

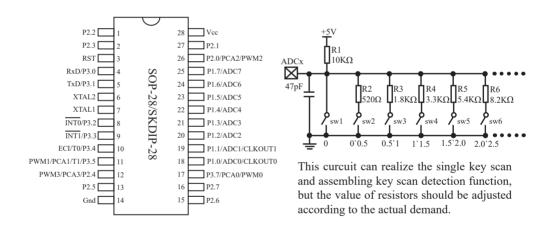

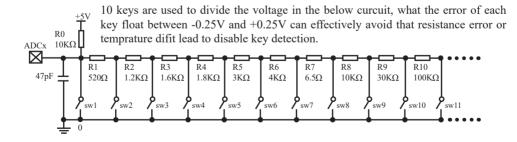

| 9.4 ADC Application Circuit for Key Scan                         |       |

| 9.5 A/D reference voltage source                                 |       |

| 9.6 Program using interrupts to demostrate A/D Conversion        |       |

| 9.7 Program using polling to demostrate A/D Conversion           |       |

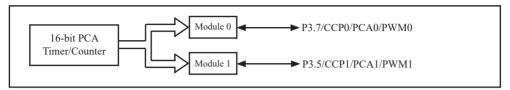

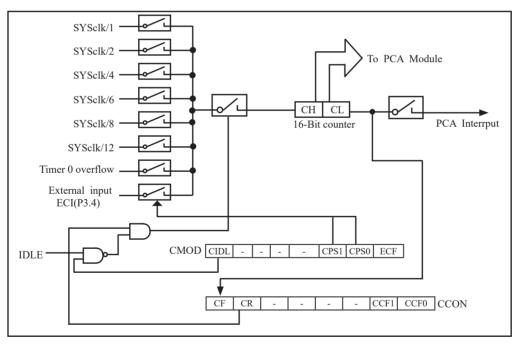

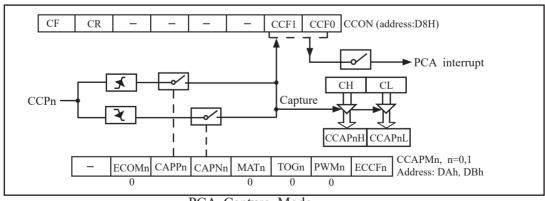

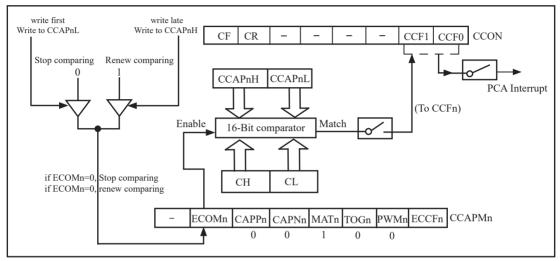

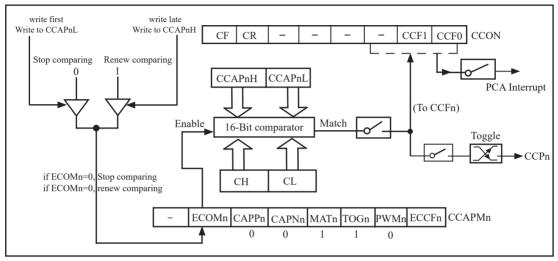

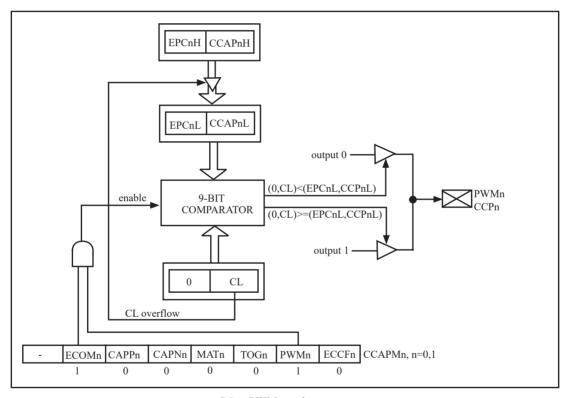

| Chapter 10. Programmable Counter Array(PCA)                      |       |

| 10.1 SFRs related with PCA                                       | 223   |

| 10.2 PCA/PWM Structure                                           | 228   |

| 10.2 PCAT WWI Structure  10.3 PCA Modules Operation Mode         | 230   |

| 10.3.1 PCA Capture Mode                                          | 230   |

| 10.3.2 16-bit Software Timer Mode                                | 231   |

| 10.3.3 High Speed Output Mode                                    | 232   |

| 10.3.4 Pulse Width Modulator Mode (PWM mode)                     |       |

| 10.4 Programs for PCA module extended external interrupt         |       |

| 10.5 Demo Programs for PCA module acted as 16-bit Timer          | . 238 |

| 10.6 Programs for PCA module as 16-bit High Speed Output         |       |

| 10.7 Demo Programs for PCA module as PWM Output                  |       |

| 10.8 Demo Program for PCA clock base on Timer 1 overflow rate    | . 250 |

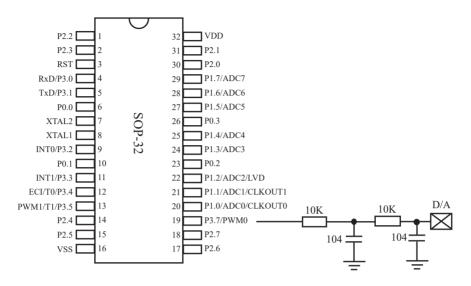

| 10.9 Using PWM achieve D/A Conversion function reference circuit | . 254 |

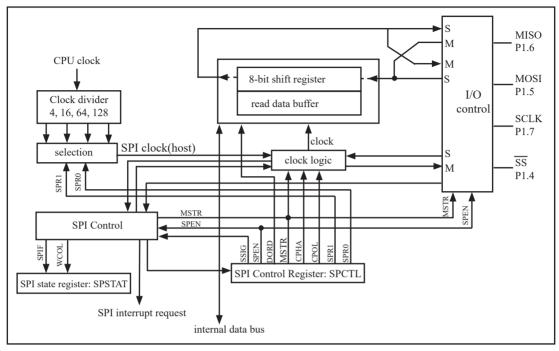

| Chapter 11. Serial Peripheral Interface (SPI)                    | .255  |

| 11.1 Special Function Registers related with SPI                 | . 255 |

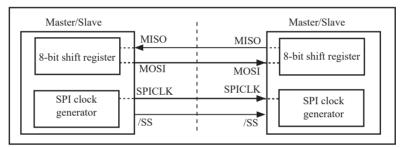

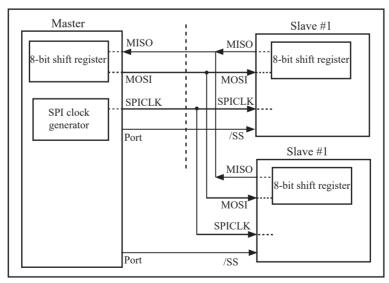

| 11.2 SPI Structure                                               | . 258 |

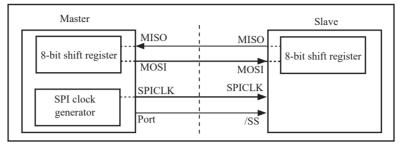

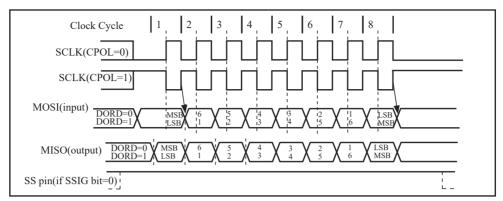

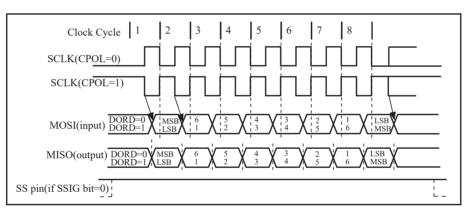

| 11.3 SPI Data Communication                                      | . 259 |

| 11.3.1 SPI Configuration                                         |       |

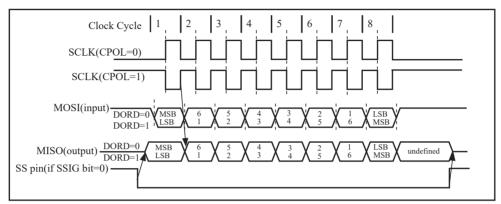

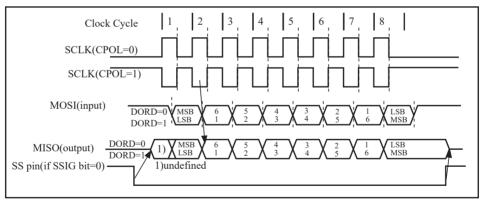

| 11.3.2 SPI Data Communication Modes                              |       |

| 11.3.3 SPI Data Modes                                            |       |

| 11.4 SPI Function Demo Programs (Single Master — Single Slave)   |       |

| 11.4.1 SPI Function Demo Programs using Interrupts (C and ASM)   |       |

| 11.4.2 SPI Function Demo Programs using Polling (C and ASM)      | 4/0   |

| 11.5 SPI Function Demo Programs (Each other as the Master-Slave) | . 276 |

|------------------------------------------------------------------|-------|

| 11.5.1 SPI Function Demo Programs using Interrupts (C and ASM)   | 276   |

| 11.5.2 SPI Function Demo Programs using Polling                  | 282   |

| Chapter 12. IAP / EEPROM                                         | 288   |

| 12.1 IAP / EEPROM Special Function Registers                     | . 289 |

| 12.2 STC12C2052AD series Internal EEPROM Allocation Table        |       |

| 12.3 IAP/EEPROM Assembly Language Program Introduction           |       |

| 12.4 EEPROM Demo Program (C and ASM)                             |       |

| Chapter 13. STC12 series Development/Programming Tool            |       |

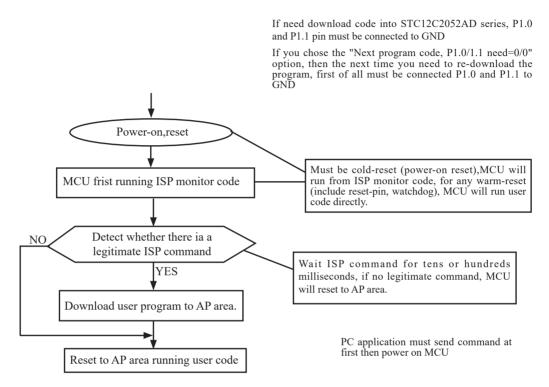

| 13.1 In-System-Programming (ISP) principle                       |       |

| 13.2 STC12C2052AD series Typical Application Circuit for ISP     |       |

| 13.3 PC side application usage                                   |       |

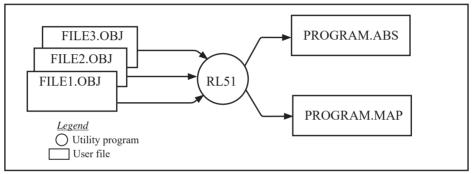

| 13.4 Compiler / Assembler Programmer and Emulator                |       |

| 13.5 Self-Defined ISP download Demo                              |       |

| Appendix A: Assembly Language Programming                        | 313   |

| Appendix B: 8051 C Programming                                   |       |

|                                                                  |       |

| Appendix C: STC12C2052AD series Electrical Characteris           |       |

| •••••                                                            | 345   |

| Appendix D: Program for indirect addressing inner 256B R         | AM    |

| ***************************************                          | 347   |

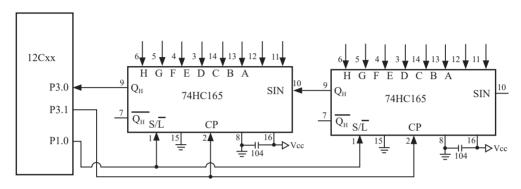

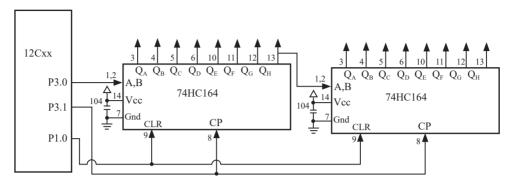

| Appendix E: Using Serial port expand I/O interface               |       |

|                                                                  |       |

| Appendix F: Use STC MCU common I/O driving LCD Dis               |       |

| ••••••                                                           | 350   |

| Appendix G: LED driven by an I/O port and Key Scan               | 357   |

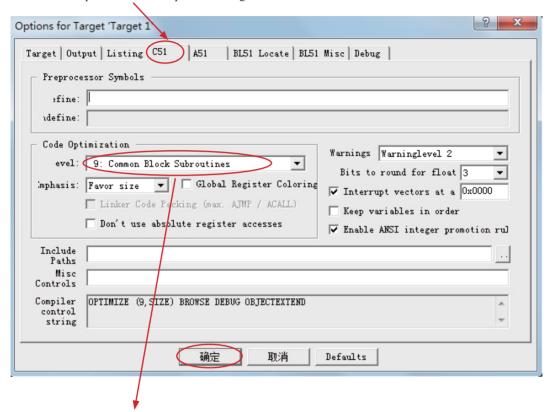

| Appendix H: How to reduce the Length of Code through K           | eil C |

|                                                                  |       |

|                                                                  |       |

| Appendix I: Notes of STC12C2052AD series Application             |       |

|                                                                  |       |

| <b>Appendix J: Notes of STC12 series Replaced Traditional 80</b> |       |

### **Chapter 1. Introduction**

STC12C2052AD is a single-chip microcontroller based on a high performance 1T architecture 8051 CPU, which is produced by STC MCU Limited. With the enhanced kernel, STC12C2052AD executes instructions in 1~6 clock cycles (about 8~12 times the rate of a standard 8051 device), and has a fully compatible instruction set with industrial-standard 8051 series microcontroller. In-System-Programming (ISP) and In-Application-Programming (IAP) support the users to upgrade the program and data in system. ISP allows the user to download new code without removing the microcontroller from the actual end product; IAP means that the device can write non-valatile data in Flash memory while the application program is running. The STC12C2052AD retains all features of the standard 80C51. In addition, the STC12C2052AD has a 9-sources, 4-priority-level interrupt structure, 8-bit ADC (100 thousands times per second), on-chip crystal oscillator, MAX810 special reset circuit, 2-channel PCA and PWM, SPI, a one-time enabled Watchdog Timer and so on.

#### 1.1 Features

- Enhanced 8051 Central Processing Unit, 1T per machine cycle, faster 8~12 times than the rate of a standard 8051.

- Operating voltage range:  $5.5V \sim 3.5V$  or  $2.2V \sim 3.6V$  (STC12LE2052AD).

- Operating frequency range: 0-35MHz, is equivalent to standard 8051:0~420MHz

- On-chip 1K/2K/3K/4K/5K... FLASH program memory with flexible ISP/IAP capability

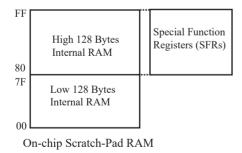

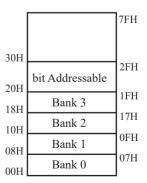

- On-chip 256 byte RAM

- Power control: idle mode(can be waked up by any interrupt) and power-down mode(can be waked up by external interrupts).

- · Code protection for flash memory access

- Excellent noise immunity, very low power consumption

- Four 16-bit timer/counter, be compatible with Timer0/Timer1 of standard 8051, 2-channel PCA can be

available as two timers.

- 9 vector-address, 4 level priority interrupt capability

- · One enhanced UART with hardware address-recognition and frame-error detection function

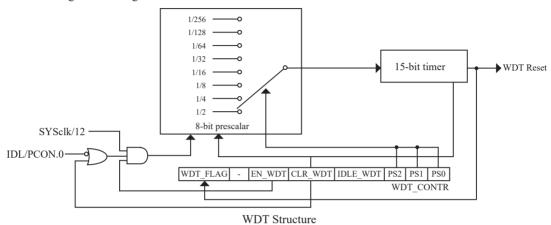

- One 15 bits Watch-Dog-Timer with 8-bit pre-scaler (one-time-enabled)

- SPI Master/Slave communication interface

- Two channel Programmable Counter Array (PCA)

- 8-bit, 8-channel high-speed Analog-to-Digital Converter (ADC), up to 100 thousands times per second

- · Simple internal RC oscillator and external crystal clock

- Three power management modes: idle mode, slow down mode and power-down mode

- Power down mode can be woken-up by P3.2/INT0, P3.3/INT1, P3.4/T0, P3.5/T1, P3.0/RxD, P3.7/PCA0, and P3.5/PCA1

- Operation Temperature:  $-40 \sim +85^{\circ}$ C (industrial)  $/0 \sim 75^{\circ}$ C (Commercial)

- 15 common programmable I/O ports are available

- Programmable clock output Function. T0 output the clock on P1.0, T1 output the clock on P1.1.

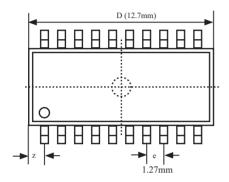

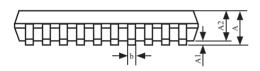

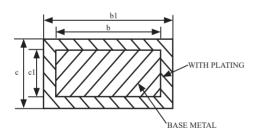

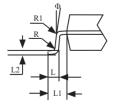

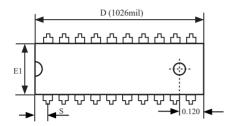

- Five package type: SOP-20, DIP-20, LSSOP-20.

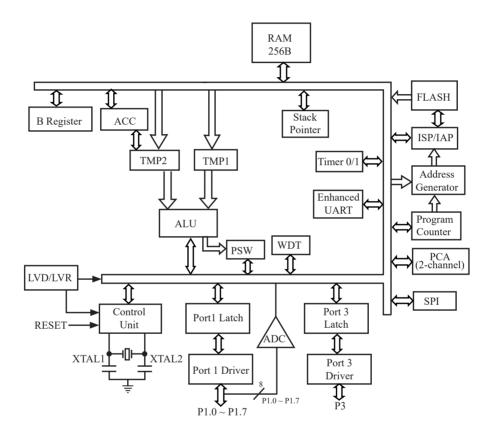

### 1.2 Block diagram

The CPU kernel of STC12C2052AD is fully compatible to the standard 8051 microcontroller, maintains all instruction mnemonics and binary compatibility. With some great architecture enhancements, STC12C2052AD executes the fastest instructions per clock cycle. Improvement of individual programs depends on the actual instructions used.

STC12C2052AD Block Diagram

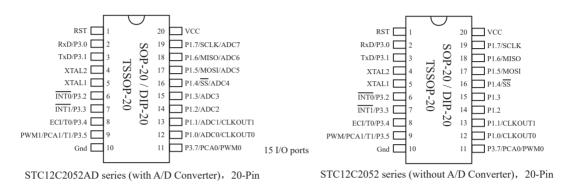

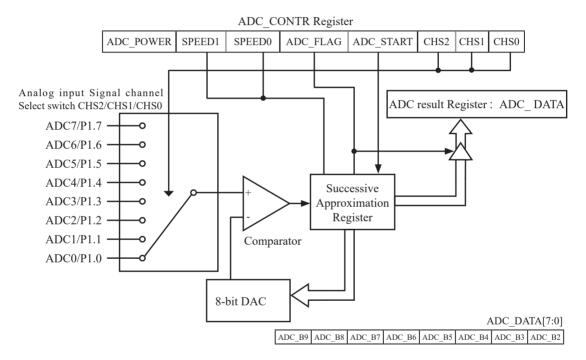

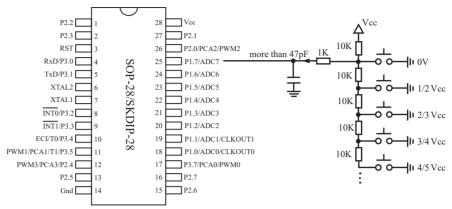

### 1.3 Pin Configurations

All packages meet the European Union RoHS standards. LQFP-32 also conform to the Green standard.

Packages such as SOP-20 are strongly recommended though the traditional DIP packages are steady supplied.

Super small package: TSSOP-20, 6.4mm×6.4mm

### 1.4 STC12C2052AD series Selection Table

| Type<br>1T 8051<br>MCU              | Operation<br>Voltage<br>(V) | Flash<br>(Byte) | SRAM<br>(Byte) | Timer<br>T0&T1 | PCA<br>Timer | Programmable<br>Clock Output | U<br>A<br>R<br>T | EEP<br>ROM | 16-bit<br>PCA/<br>8-bit<br>PWM<br>D/A | A/D<br>8-ch | W<br>D<br>T | Built-in<br>Reset | SPI | Package of 20-Pin<br>(15 I/O ports)                         |

|-------------------------------------|-----------------------------|-----------------|----------------|----------------|--------------|------------------------------|------------------|------------|---------------------------------------|-------------|-------------|-------------------|-----|-------------------------------------------------------------|

| STC12C2052AD series Selection Table |                             |                 |                |                |              |                              |                  |            |                                       |             |             |                   |     |                                                             |

| STC12C1052                          | 5.5-3.5                     | 1K              | 256            | Y              | 2            | Y                            | Y                | Y          | 2-ch                                  |             | Y           | Y                 | Y   | SOP/LSSOP/DIP                                               |

| STC12C1052AD                        | 5.5-3.5                     | 1K              | 256            | Y              | 2            | Y                            | Y                | Y          | 2-ch                                  | 8-bit       | Y           | Y                 | Y   | SOP/LSSOP/DIP                                               |

| STC12C2052                          | 5.5-3.5                     | 2K              | 256            | Y              | 2            | Y                            | Y                | Y          | 2-ch                                  |             | Y           | Y                 | Y   | SOP/LSSOP/DIP                                               |

| STC12C2052AD                        | 5.5-3.5                     | 2K              | 256            | Y              | 2            | Y                            | Y                | Y          | 2-ch                                  | 8-bit       | Y           | Y                 | Y   | SOP/LSSOP/DIP                                               |

| STC12C3052                          | 5.5-3.5                     | 3K              | 256            | Y              | 2            | Y                            | Y                | IAP        | 2-ch                                  |             | Y           | Y                 | Y   | SOP/LSSOP/DIP                                               |

| STC12C3052AD                        | 5.5-3.5                     | 3K              | 256            | Y              | 2            | Y                            | Y                | Y          | 2-ch                                  | 8-bit       | Y           | Y                 | Y   | SOP/LSSOP/DIP                                               |

| STC12C4052                          | 5.5-3.5                     | 4K              | 256            | Y              | 2            | Y                            | Y                | Y          | 2-ch                                  |             | Y           | Y                 | Y   | SOP/LSSOP/DIP                                               |

| STC12C4052AD                        | 5.5-3.5                     | 4K              | 256            | Y              | 2            | Y                            | Y                | Y          | 2-ch                                  | 8-bit       | Y           | Y                 | Y   | SOP/LSSOP/DIP                                               |

| STC12C5052                          | 5.5-3.5                     | 5K              | 256            | Y              | 2            | Y                            | Y                | Y          | 2-ch                                  |             | Y           | Y                 | Y   | Application program                                         |

| STC12C5052AD                        | 5.5-3.5                     | 6K              | 256            | Y              | 2            | Y                            | Y                | Y          | 2-ch                                  | 8-bit       | Y           | Y                 | Y   | can be modified in<br>application program<br>area (AP area) |

|                                     |                             |                 |                | ST             | C12LE2       | 2052AD series S              | ele              | ction Ta   | ıble                                  |             |             |                   |     |                                                             |

| STC12LE1052                         | 3.6-2.2                     | 1K              | 256            | Y              | 2            | Y                            | Y                | Y          | 2-ch                                  |             | Y           | Y                 | Y   | SOP/LSSOP/DIP                                               |

| STC12LE1052AD                       | 3.6-2.2                     | 1K              | 256            | Y              | 2            | Y                            | Y                | Y          | 2-ch                                  | 8-bit       | Y           | Y                 | Y   | SOP/LSSOP/DIP                                               |

| STC12LE2052                         | 3.6-2.2                     | 2K              | 256            | Y              | 2            | Y                            | Y                | Y          | 2-ch                                  |             | Y           | Y                 | Y   | SOP/LSSOP/DIP                                               |

| STC12LE2052AD                       | 3.6-2.2                     | 2K              | 256            | Y              | 2            | Y                            | Y                | Y          | 2-ch                                  | 8-bit       | Y           | Y                 | Y   | SOP/LSSOP/DIP                                               |

| STC12LE3052                         | 3.6-2.2                     | 3K              | 256            | Y              | 2            | Y                            | Y                | Y          | 2-ch                                  |             | Y           | Y                 | Y   | SOP/LSSOP/DIP                                               |

| STC12LE3052AD                       | 3.6-2.2                     | 3K              | 256            | Y              | 2            | Y                            | Y                | Y          | 2-ch                                  | 8-bit       | Y           | Y                 | Y   | SOP/LSSOP/DIP                                               |

| STC12LE4052                         | 3.6-2.2                     | 4K              | 256            | Y              | 2            | Y                            | Y                | Y          | 2-ch                                  |             | Y           | Y                 | Y   | SOP/LSSOP/DIP                                               |

| STC12LE4052AD                       | 3.6-2.2                     | 4K              | 256            | Y              | 2            | Y                            | Y                | Y          | 2-ch                                  | 8-bit       | Y           | Y                 | Y   | SOP/LSSOP/DIP                                               |

| STC12LE5052                         | 3.6-2.2                     | 5K              | 256            | Y              | 2            | Y                            | Y                | Y          | 2-ch                                  |             | Y           | Y                 | Y   | Application program                                         |

| STC12LE5052AD                       | 3.6-2.2                     | 5K              | 256            | Y              | 2            | Y                            | Y                | Y          | 2-ch                                  | 8-bit       | Y           | Y                 | Y   | can be modified in<br>application program<br>area (AP area) |

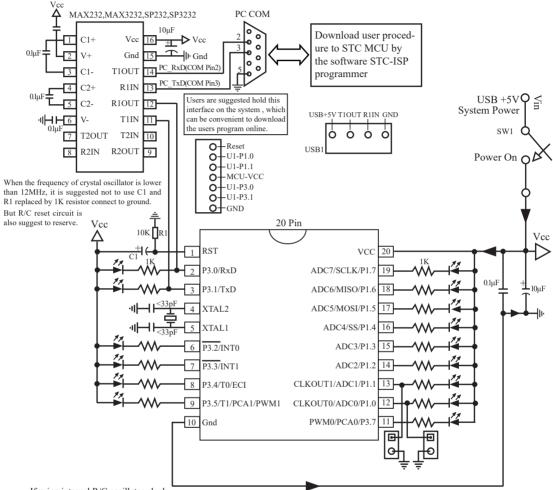

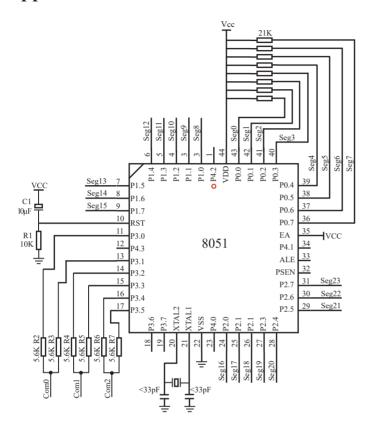

### 1.5 STC12C2052AD series Minimum Application System

When the frequency of crystal oscillator is lower than 12MHz, it is suggested not to use C1 and R1 replaced by 1K resistor connect to ground.

But R/C reset circuit is also suggest to reserve.

RST VCC 20 System power/5V/3V Power On SW1 10K P3.0/RxD ADC7/SCLK/P1.7 19 C6 C2<33pF P3.1/TxD ADC6/MISO/P1.6 18 0.1μF  $10\mu F$ ADC5/MOSI/P1.5 17 XTAL2 ADC4/SS/P1.4 16 XTAL1 C3<33pF ADC3/P1.3 15 P3.2/INT0 P3.3/INT1 ADC2/P1.2 14 P3.4/T0/ECI CLKOUT1/ADC1/P1.1 13 9 P3.5/T1/PCA1/PWM1 CLKOUT0/ADC0/P1.0 12

#### About crystals circuit:

10

If using internal R/C oscillator clock (4MHz  $\sim$  8MHz, manufacturing error), XTAL1 and XTAL2 pin should be floated.

PWM0/PCA0/P3.7 11

If External clock frequency is higher than 33MHz, it is recommended to directly use external active crystals which clock are input from XTAL1 pin and XTAL2 pin must be floated.

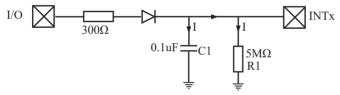

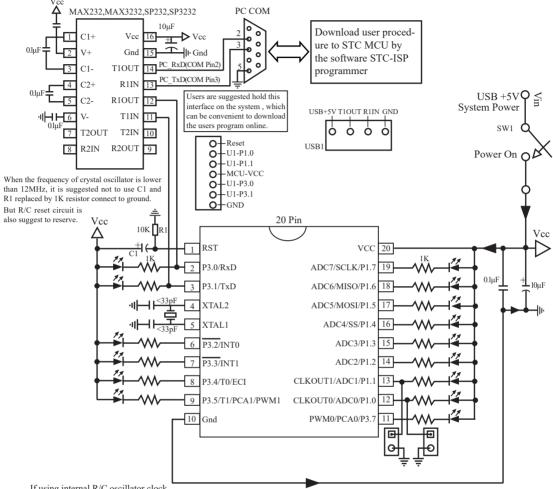

### 1.6 STC12C2052AD series MCU Typical Application Circuit for ISP

—— MCU should be connected to computer through RS-232 converter to download program

If using internal R/C oscillator clock (4MHz ~ 8MHz, manufacturing error), XTAL1 and XTAL2 pin should be floated.

If External clock frequency is higher than 33MHz, it is recommended to directly use external active crystals which clock are input from XTAL1 pin and XTAL2 pin must be floated.

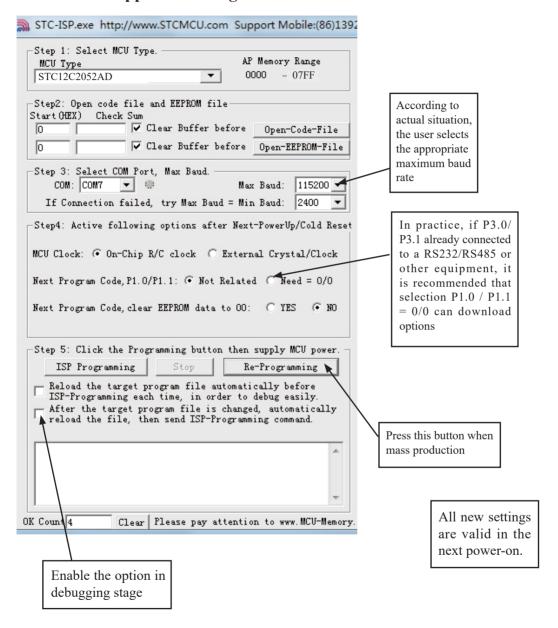

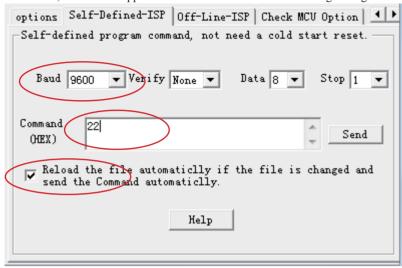

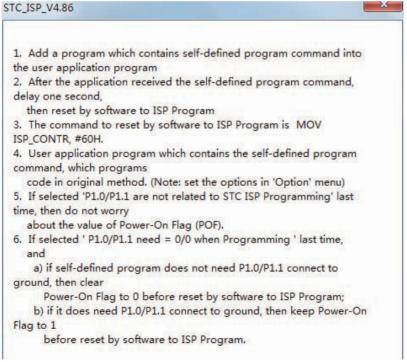

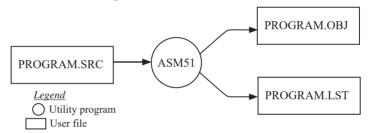

This circuit has been made as a STC12C2052AD series microcontroller ISP download programming tool