# STC15W1K20S-LQFP64单片机总体介绍

## 1 STC15W1K20S-LQFP64单片机简介

STC15W1K20S-LQFP64单片机是STC生产的单时钟/机器周期(1T)的单片机，是宽电压/高速/高可靠/低功耗/超强抗干扰的新一代8051单片机，采用STC第九代加密技术，无法解密，指令代码完全兼容传统8051，但速度快8-12倍。内部集成高精度R/C时钟( $\pm 0.3\%$ )， $\pm 1\%$ 温飘(-40°C ~ +85°C)，常温下温飘 $\pm 0.6\%$ (-20°C ~ +65°C)，ISP编程时5MHz~35MHz宽范围可设置，可彻底省掉外部昂贵的晶振和外部复位电路(内部已集成高可靠复位电路，ISP编程时16级复位门槛电压可选)。3个16位定时器/计数器，1个掉电唤醒定时器，双数据指针，内置1K字节大容量SRAM，1组高速异步串行通信口(UART，可在3组管脚之间进行切换，分时复用可作3组串口使用)，1组高速同步串行通信端口SPI，针对麻将机市场。内置比较器，功能更强大。

在 Keil C 开发环境中，选择 Intel 8052 编译，头文件包含<reg51.h>即可

现STC15系列单片机采用STC-Y5超高速CPU内核，在相同的时钟频率下，速度又比STC早期的1T系列单片机(如STC12系列/STC11系列/STC10系列)的速度快20%.

1. 增强型 8051 CPU, 1T, 单时钟/机器周期，速度比普通8051快8-12倍

2. 工作电压: 2.5V - 5.5V

3. 20K字节片内Flash程序存储器，擦写次数10万次以上

4. 片内集成1024字节的SRAM，包括常规的256字节RAM <idata> 和内部扩展的768字节 XRAM <xdata>

5. 有片内EEPROM功能，擦写次数10万次以上

6. ISP/IAP，在系统可编程/在应用可编程，无需编程器/仿真器

7. 内部高可靠复位，ISP编程时16级复位门槛电压可选，可彻底省掉外部复位电路

8. 工作频率范围: 5MHz ~ 28MHz，相当于普通8051的60MHz~336MHz

9. 内部高精度R/C时钟( $\pm 0.3\%$ )， $\pm 1\%$ 温飘(-40°C ~ +85°C)，常温下温飘 $\pm 0.6\%$ (-20°C ~ +65°C)，ISP编程时内部时钟从5MHz~35MHz可设(5.5296MHz / 11.0592MHz / 22.1184MHz / 33.1776MHz)

**10.不需外部晶振和外部复位，还可对外输出时钟和低电平复位信号**

11.一组高速异步串行通信端口UART，可在3组管脚之间切换，分时复用可当3组串口使用：

串行口(RxD/P3.0, TxD/P3.1)可以切换到(RxD\_2/P3.6, TxD\_2/P3.7),

还可以切换到(RxD\_3/P1.6, TxD\_3/P1.7)；

**注意：建议用户将串口放在[P3.6/RxD\_2, P3.7/TxD\_2]或[P1.6/RxD\_3, P1.7/TxD\_3]上([P3.0, P3.1]作下载/仿真用)；若用户未将串口切换到[P3.6/RxD\_2, P3.7/TxD\_2]或[P1.6/RxD\_3, P1.7/TxD\_3]，而是用[P3.0/RxD, P3.1/TxD]作串口，则务必在ISP编程时在STC-ISP软件的硬件选项中勾选“下次冷启动时，P3.2/P3.3为0/0时才可以下载程序”**

12.一组高速同步串行通信端口SPI

**13.支持程序加密后传输，防拦截**

**14.支持RS485下载**

**15.支持USB直接下载**

16.低功耗设计：低速模式，空闲模式，掉电模式/停机模式。

17.可将掉电模式/停机模式唤醒的定时器：**有内部低功耗掉电唤醒专用定时器。**

18.可将掉电模式/停机模式唤醒的资源有：INT0/P3.2, INT1/P3.3 (INT0/INT1上升沿下降沿中断均可), INT2 /P3.6, INT3 /P3.7, INT4 /P3.0(INT2 / INT3/INT4仅可下降沿中断)；管脚RxD(可在RxD/P3.0、RxD\_2/P3.6和RxD\_3/P1.6之间切换)；管脚T0/T1/T2(下降沿，不产生中断，前提是在进入掉电模式/停机模式前相应的定时器中断已经被允许)；内部低功耗掉电唤醒专用定时器。

19.共3个定时器/计数器，3个16位可重装载的定时器/计数器(T0/T1/T2，其中T0/T1兼容普通8051的定时器/计数器)，并都可实现可编程时钟输出，另外管脚SysClkO可将系统时钟对外分频输出( $\div 1$ 或 $\div 2$ 或 $\div 4$ 或 $\div 16$ )。

20.可编程时钟输出功能(对内部系统时钟或对外部管脚的时钟输入进行时钟分频输出)：

**由于STC15系列5V单片机I/O口的对外输出速度最快不超过13.5MHz，所以5V单片机的对外可编程时钟输出速度最快也不超过13.5MHz.;**

**而3.3V单片机I/O口的对外输出速度最快不超过8MHz，故3.3V单片机的对外可编程时钟输出速度最快也不超过8MHz.**

① T0在P3.5/T0CLKO进行可编程输出时钟(对内部系统时钟或对外部管脚T0/P3.4的时钟输入进行可编程时钟分频输出)；

② T1在P3.4/T1CLKO进行可编程输出时钟(对内部系统时钟或对外部管脚T1/P3.5的时钟输入进行可编程时钟分频输出)；

③ T2在P3.0/T2CLKO进行可编程输出时钟(对内部系统时钟或对外部管脚T2/P3.1的时钟输入进行可编程时钟分频输出)；

以上3个定时器/计数器均可1~65536级分频输出。

- ④ 系统时钟在P5.4/SysClkO或P1.6/XTAL2/SysClkO\_2对外输出时钟，并可如下分频

SysClk/1, SysClk/2, SysClk/4, SysClk/16.

系统时钟是指对主时钟进行分频后供给CPU、串行口、SPI、定时器的实际工作时钟；主时钟可以是内部R/C时钟，也可以是外部输入的时钟或外部晶体振荡产生的时钟；SysClk是指系统时钟频率，SysClkO是指系统时钟输出。

STC15系列中除STC15W401AS系列、STC15W4K32S4系列、STC15W1K08PWM系列及STC15W1K20S-LQFP64单片机是将系统时钟对外分频输出外，其他系列单片机均是将主时钟对外分频输出。

21. 比较器，可当1路ADC使用，并可作掉电检测，支持外部管脚CMP+与外部管脚CMP-进行比较，可产生中断，并可在管脚CMPO上产生输出（可设置极性），也支持外部管脚CMP+与内部参考电压进行比较

若[P5.5/CMP+, P5.4/CMP-]被用作比较器正极(CMP+)/负极(CMP-)，则[P5.5/CMP+, P5.4/CMP-]要被设置为高阻输入

22. 硬件看门狗(WDT)

23. 先进的指令集结构，兼容普通8051指令集，有硬件乘法/除法指令

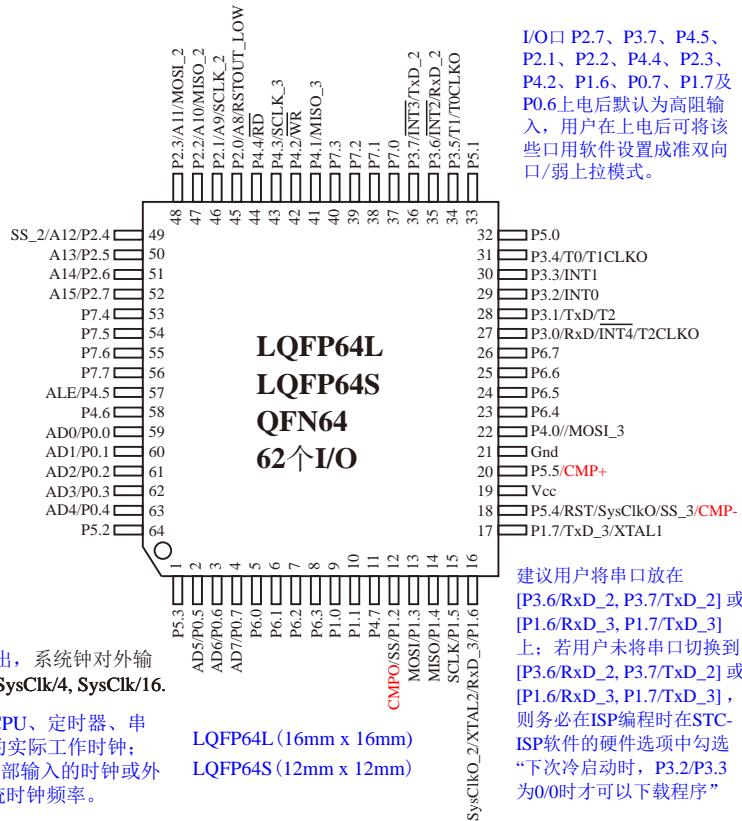

24. 通用I/O口(62个)，复位后为：准双向口/弱上拉（普通8051传统I/O口）

可设置成四种模式：准双向口/弱上拉，强推挽/强上拉，仅为输入/高阻，开漏

每个I/O口驱动能力均可达到20mA，但整个芯片电流最大不要超过90mA.

如果I/O口不够用，可外接74HC595(参考价0.15元)来扩展I/O口，并可多芯片级联扩展几十个I/O口。

25. 封装：LQFP64S(12mm x 12mm), LQFP64L(16mm x 16mm).

26. 全部175°C八小时高温烘烤，高品质制造保证

27. 开发环境：在 Keil C 开发环境中，选择 Intel 8052 编译，头文件包含<reg51.h>即可

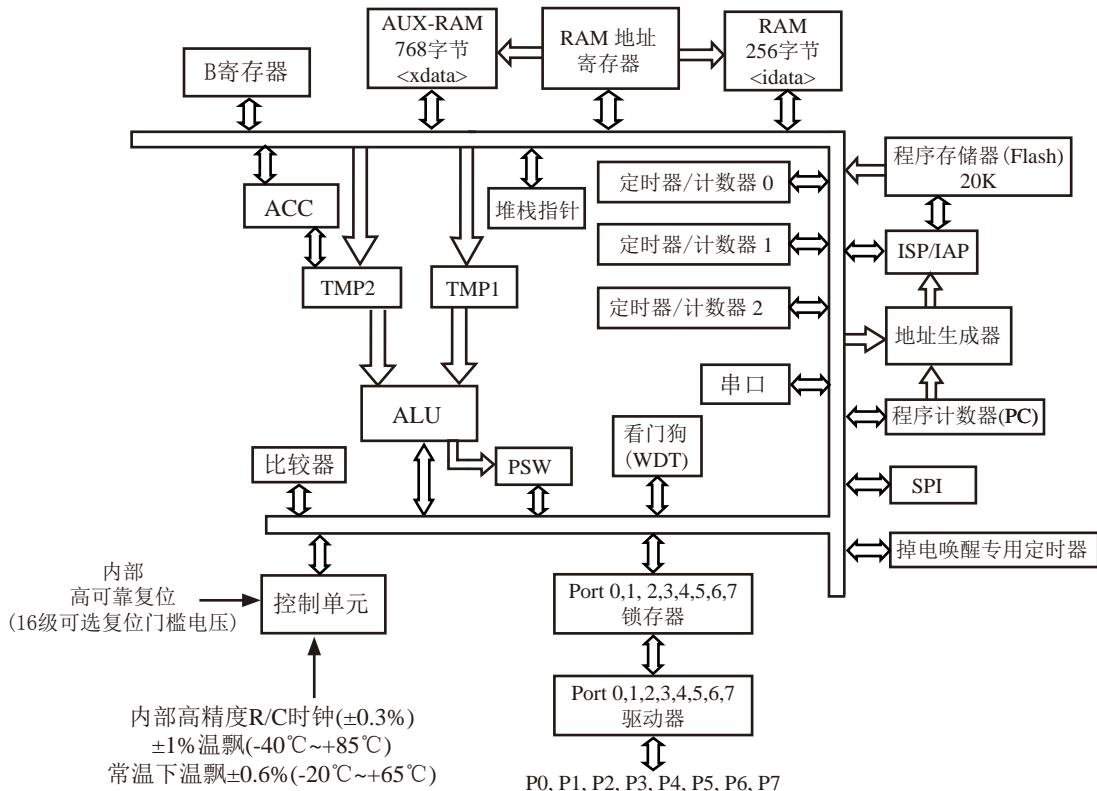

## 2 STC15W1K20S-LQFP64单片机的内部结构图

STC15W1K20S-LQFP64单片机的内部结构框图如下图所示。STC15W1K20S-LQFP64单片机中包含中央处理器(CPU)、程序存储器(Flash)、数据存储器(SRAM)、定时器/计数器、内部掉电唤醒专用定时器、I/O口、比较器、看门狗、高速异步串行通信端口UART、高速同步串行端口SPI，片内高精度R/C时钟及高可靠复位等模块。STC15W1K20S-LQFP64单片机几乎包含了数据采集和控制中所需要的所有单元模块，可称得上是一个片上系统(SysTem Chip或SysTem on Chip，简写为STC，这是宏晶科技STC名称的由来)。

STC15W1K20S-LQFP64内部结构框图

### 3 STC15W1K20S-LQFP64单片机管脚图

T0CLKO是指定时器/计数器0的可编程时钟输出(对内部系统时钟或对外部管脚T0/P3.4的时钟输入进行可编程时钟分频输出);

T1CLKO是指定时器/计数器1的可编程时钟输出(对内部系统时钟或对外部管脚T1/P3.5的时钟输入进行可编程时钟分频输出);

T2CLKO是指定时器/计数器2的可编程时钟输出(对内部系统时钟或对外部管脚T2/P3.1的时钟输入进行可编程时钟分频输出);

T0CLKO/T1CLKO/T2CLKO除可以对内部系统时钟进行可编程时钟输出外，还可以对外部管脚T0/T1/T2的时钟输入进行时钟分频输出，作分频器使用。

对于STC15系列5V单片机，由于I/O口的对外输出速度最快不超过13.5MHz，所以对外可编程时钟输出速度最快也不超过13.5MHz；

对于3.3V单片机，由于I/O口的对外输出速度最快不超过8MHz，所以对外可编程时钟输出速度最快也不超过8MHz；

SysClkO\_2与SysClkO均是指系统时钟输出，系统时钟对外输出的时钟可如下分频SysClk/1, SysClk/2, SysClk/4, SysClk/16.

系统时钟是指对主时钟进行分频后供给CPU、定时器、串行口、SPI、CCP/PWM/PCA、A/D转换的实际工作时钟；主时钟可以是内部R/C时钟，也可以是外部输入的时钟或外部晶体振荡产生的时钟；`SysClk`是指系统时钟频率。

| Mnemonic                  | Add | Name                 | B7        | B6        | B5   | B4    | B3        | B2     | B1     | B0     | Reset Value  |

|---------------------------|-----|----------------------|-----------|-----------|------|-------|-----------|--------|--------|--------|--------------|

| AUXR1<br><b>P_SW1</b>     | A2H | Auxiliary register 1 | S1_S1     | S1_S0     | -    | -     | SPI_S1    | SPI_S0 | 0      | DPS    | 00xx<br>0000 |

| <b>CLK_DIV</b><br>(PCON2) | 97H | 时钟分频寄存器              | SysCKO_S1 | SysCKO_S0 | ADRJ | Tx_Rx | SysClkO_2 | CLKS2  | CLKS1  | CLKS0  | 0000<br>0000 |

| INT_CLKO<br>(AUXR2)       | 8FH | 外部中断允许并时钟输出          | -         | EX4       | EX3  | EX2   | SysCKO_S2 | T2CLKO | T1CLKO | T0CLKO | x000<br>0000 |

串口1/S1可在3个地方切换，由 S1\_S0 及 S1\_S1 控制位来选择

| 串口1/S1可在3个地方切换，由 S1_S0 及 S1_S1 控制位来选择 |       |                                                               |

|---------------------------------------|-------|---------------------------------------------------------------|

| S1_S1                                 | S1_S0 | 串口1/S1可在P1/P3之间来回切换                                           |

| 0                                     | 0     | 串口1/S1在[P3.0/RxD,P3.1/TxD]                                    |

| 0                                     | 1     | 串口1/S1在[P3.6/RxD_2,P3.7/TxD_2]                                |

| 1                                     | 0     | 串口1/S1在[P1.6/RxD_3/XTAL2,P1.7/TxD_3/XTAL1]<br>串口1在P1口时要使用内部时钟 |

| 1                                     | 1     | 无效                                                            |

串口1建议放在[P3.6/RxD\_2,P3.7/TxD\_2]或[P1.6/RxD\_3/XTAL2,P1.7/TxD\_3/XTAL1]上。

建议用户在程序中将[S1\_S1, S1\_SO]的值设置为[0, 1]或[1, 0], 进而将串口1放在[P3.6/RxD\_2, P3.7/TxD\_2]或[P1.6/RxD\_3/XTAL2, P1.7/TxD\_3/XTAL1]上

| Mnemonic                 | Add | Name                 | B7        | B6        | B5   | B4    | B3        | B2     | B1     | B0     | Reset Value |

|--------------------------|-----|----------------------|-----------|-----------|------|-------|-----------|--------|--------|--------|-------------|

| AUXR1<br><b>P_SW1</b>    | A2H | Auxiliary register 1 | S1_S1     | S1_S0     | -    | -     | SPI_S1    | SPI_S0 | 0      | DPS    | 00xx 0000   |

| <b>CLK_DIV</b><br>(PCON) | 97H | 时钟分频寄存器              | SysCKO_S1 | SysCKO_S0 | ADRJ | Tx_Rx | SysClkO_2 | CLKS2  | CLKS1  | CLKS0  | 0000 0000   |

| INT_CLKO<br>(AUXR2)      | 8FH | 外部中断允许并时钟输出          | -         | EX4       | EX3  | EX2   | SysCKO_S2 | T2CLKO | T1CLKO | T0CLKO | x000 0000   |

|                                        |        |                                                     |

|----------------------------------------|--------|-----------------------------------------------------|

| SPI可在3个地方切换，由 SPI_S1 / SPI_S0 两个控制位来选择 |        |                                                     |

| SPI_S1                                 | SPI_S0 | SPI可在P1/P2/P4之间来回切换                                 |

| 0                                      | 0      | SPI在[P1.2/SS,P1.3/MOSI,P1.4/MISO,P1.5/SCLK]         |

| 0                                      | 1      | SPI在[P2.4/SS_2,P2.3/MOSI_2,P2.2/MISO_2,P2.1/SCLK_2] |

| 1                                      | 0      | SPI在[P5.4/SS_3,P4.0/MOSI_3,P4.1/MISO_3,P4.3/SCLK_3] |

| 1                                      | 1      | 无效                                                  |

**DPS: DPTR registers select bit.** DPTR 寄存器选择位

0: DPTR0 is selected DPTR0被选择

1: DPTR1 is selected DPTR1被选择

|           |           |           |                                                              |

|-----------|-----------|-----------|--------------------------------------------------------------|

| SysCKO_S2 | SysCKO_S1 | SysCKO_S0 | 系统时钟时钟对外分频输出控制位<br>(系统时钟是指对主时钟进行分频后供给CPU、串行口、SPI、定时器的实际工作时钟) |

| 0         | 0         | 0         | 系统时钟不对外输出时钟                                                  |

| 0         | 0         | 1         | 系统时钟对外输出时钟，但时钟频率不被分频，输出时钟频率 = SysClk / 1                     |

| 0         | 1         | 0         | 系统时钟对外输出时钟，但时钟频率被2分频，输出时钟频率 = SysClk / 2                     |

| 0         | 1         | 1         | 系统时钟对外输出时钟，但时钟频率被4分频，输出时钟频率 = SysClk / 4                     |

| 1         | 0         | 0         | 系统时钟对外输出时钟，但时钟频率被16分频，输出时钟频率 = SysClk / 16                   |

主时钟可以是内部R/C时钟，也可以是外部输入的时钟或外部晶体振荡产生的时钟； **SysClk**是指系统时钟频率。

STC15系列中除STC15W1K08PWM系列、STC15W4K32S4系列、STC15W401AS系列及STC15W1K20S-LQFP64单片机是将系统时钟对外分频输出外，其他系列单片机均是将**主时钟对外分频输出**。

STC15W1K20S-LQFP64单片机通过CLK\_DIV.3/SysClkO\_2位来选择是在SysClkO/P5.4口对外输出时钟，还是在SysClkO\_2/P1.6口对外输出时钟。

**SysClkO\_2:** 系统时钟对外输出位置的选择位

0: 在SysClkO/P5.4口对外输出时钟；

1: 在SysClkO\_2/XTAL2/P1.6口对外输出时钟。

系统时钟是指对主时钟进行分频后供给CPU、定时器、串行口、SPI的实际工作时钟； 主时钟可以是内部R/C时钟，也可以是外部输入的时钟或外部晶体振荡产生的时钟。

| Mnemonic                  | Add | Name                 | 7       | 6       | 5      | 4      | 3       | 2      | 1     | 0     | Reset Value |

|---------------------------|-----|----------------------|---------|---------|--------|--------|---------|--------|-------|-------|-------------|

| AUXR1<br><b>P_SW1</b>     | A2H | Auxiliary register 1 | S1_S1   | S1_S0   | CCP_S1 | CCP_S0 | SPI_S1  | SPI_S0 | 0     | DPS   | 0000 0000   |

| <b>CLK_DIV</b><br>(PCON2) | 97H | 时钟分频寄存器              | MCKO_S1 | MCKO_S0 | ADRJ   | Tx_Rx  | MCLKO_2 | CLKS2  | CLKS1 | CLKS0 | 0000 0000   |

**Tx\_Rx:** 串口1的中继广播方式设置

0: 串口1为正常工作方式

1: 串口1为中继广播方式, 即将RxD端口输入的电平状态实时输出在TxD外部管脚上, TxD外部管脚可以对RxD管脚的输入信号进行实时整形放大输出, TxD管脚的对外输出实时反映RxD端口输入的电平状态。

串口1的RxD管脚和TxD管脚可以在3组不同管脚之间进行切换: [RxD/P3.0, TxD/P3.1];

[RxD\_2/P3.6, TxD\_2/P3.7];

[RxD\_3/P1.6, TxD\_3/P1.7].

| CLKS2 | CLKS1 | CLKS0 | 系统时钟选择控制位                                 |

|-------|-------|-------|-------------------------------------------|

|       |       |       | (系统时钟是指对主时钟进行分频后供给CPU、串行口、SPI、定时器的实际工作时钟) |

| 0     | 0     | 0     | 主时钟频率/1,不分频                               |

| 0     | 0     | 1     | 主时钟频率/2                                   |

| 0     | 1     | 0     | 主时钟频率/4                                   |

| 0     | 1     | 1     | 主时钟频率/8                                   |

| 1     | 0     | 0     | 主时钟频率/16                                  |

| 1     | 0     | 1     | 主时钟频率/32                                  |

| 1     | 1     | 0     | 主时钟频率/64                                  |

| 1     | 1     | 1     | 主时钟频率/128                                 |

主时钟可以是内部R/C时钟, 也可以是外部输入的时钟或外部晶体振荡产生的时钟。

## 4 STC15W1K20S-LQFP64单片机选型价格一览表

| 型号                      | 工作电压(V) | Flash程序存储器(byte) | 大容量SRAM字节 | 串行口并行I/O | 掉电唤醒 | 普通定时器计数器 | CCP PCA PWM | 掉电唤醒专用定时器 | 标准外部中断 | A/D 8路 | 比较器(可当1路使用) | D/A | EEPROM | 内部低压检测 | 内部高可靠复位看门狗 | 内部高精度复位看门狗 | 可对外输出时钟及复位 | 程序加密后传输防截获命令 | 可设下次更新程序 | 支持RS485 | 支持USB | 所有封装LQFP64S/LQFP64L(62个I/O口) |      |      |

|-------------------------|---------|------------------|-----------|----------|------|----------|-------------|-----------|--------|--------|-------------|-----|--------|--------|------------|------------|------------|--------------|----------|---------|-------|------------------------------|------|------|

|                         |         |                  |           |          |      |          |             |           |        |        |             |     |        |        |            |            |            |              |          |         |       | 封装价格(RMB ¥)                  |      |      |

| STC15W1K16S系列单片机选型价格一览表 |         |                  |           |          |      |          |             |           |        |        |             |     |        |        |            |            |            |              |          |         |       |                              |      |      |

| STC15W1K20S             | 5.5-2.5 | 20K              | 1K        | 1        | 有    | 3        | -           | 有         | 5      | -      | 有           | 2   | 6K     | 有      | 有          | 16级        | 有          | 是            | 有        | 是       | 是     | 是                            | ¥3.8 | ¥4.0 |

**程序加密后传输：** 程序拥有者产品出厂时将源程序和加密钥匙一起烧录MCU中，以后需要升级软件时，就可将程序加密后再用“发布项目程序”功能，生成一个用户自己界面的只有一个升级按钮的简单易用的升级软件，给最终使用者自己升级，而拦截不到您的原始程序。

### 提供定制化IC服务

如果用户要用40-pin及以上的单片机，建议选用LQFP44的封装，但PDIP40封装仍正常供货；如果用户要用32-pin单片机，建议用户选用LQFP32封装；如果用户要用28-pin单片机，建议用户选用SOP28封装。

因为程序区的最后7个字节单元被强制性的放入全球唯一ID号的内容，所以用户实际可以使用的程序空间大小要比选型表中的大小少7个字节。

若[P5.5/CMP+, P5.4/CMP-]被用作比较器正极(CMP+)/负极(CMP-)，则[P5.5/CMP+, P5.4/CMP-]要被设置为高阻输入

总结：STC15W1K20S-LQFP64单片机有：3普通定时器/计数器(这3个普通定时器/计数器是指：T0、T1和T2)；掉电唤醒专用定时器；5个支持掉电唤醒的外部中断INT0/INT1/INT2/INT3/INT4；1组高速异步串行通信端口；1个比较器；2个数据指针DPTR等功能。

我们直销，所以低价

以上单价为10K起订

量小每片需加0.1元

以上价格运费由客户承担，零售10片起

如对价格不满，可来电要求降价

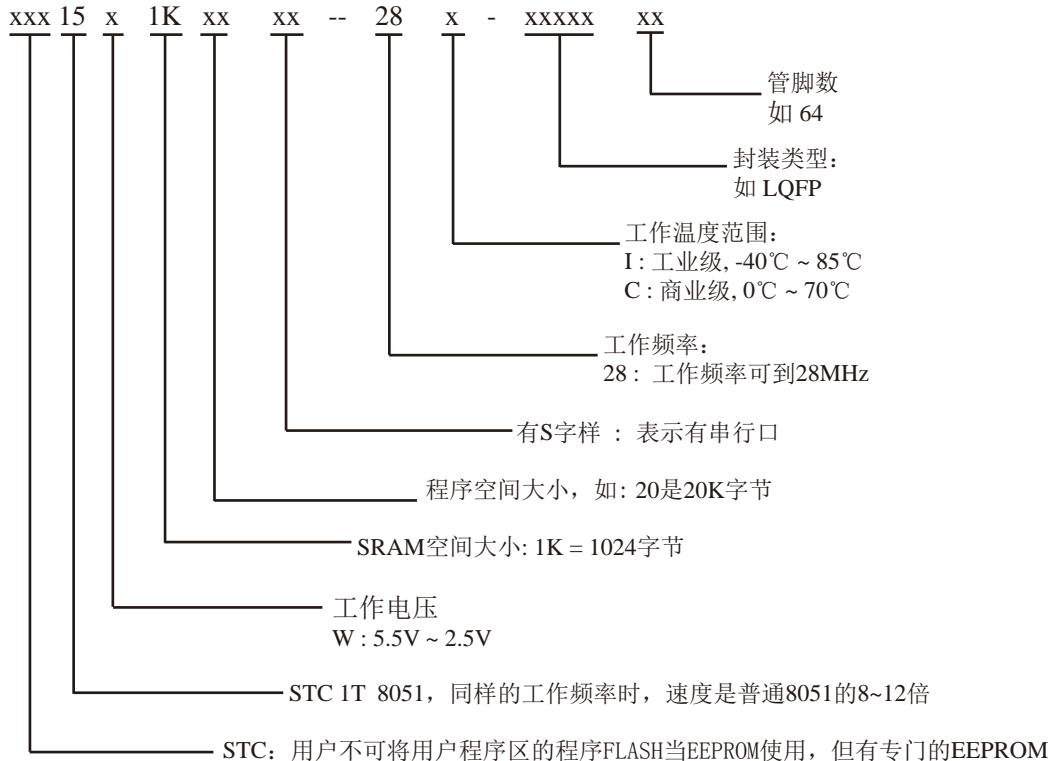

## 5 STC15W1K20S-LQFP64单片机命名规则

※ 如何识别芯片版本号: 如需知道芯片版本号, 请查阅芯片表面印刷字中最下面一行的最后一个字母 (如A), 该字母代表芯片版本号 (如A版)

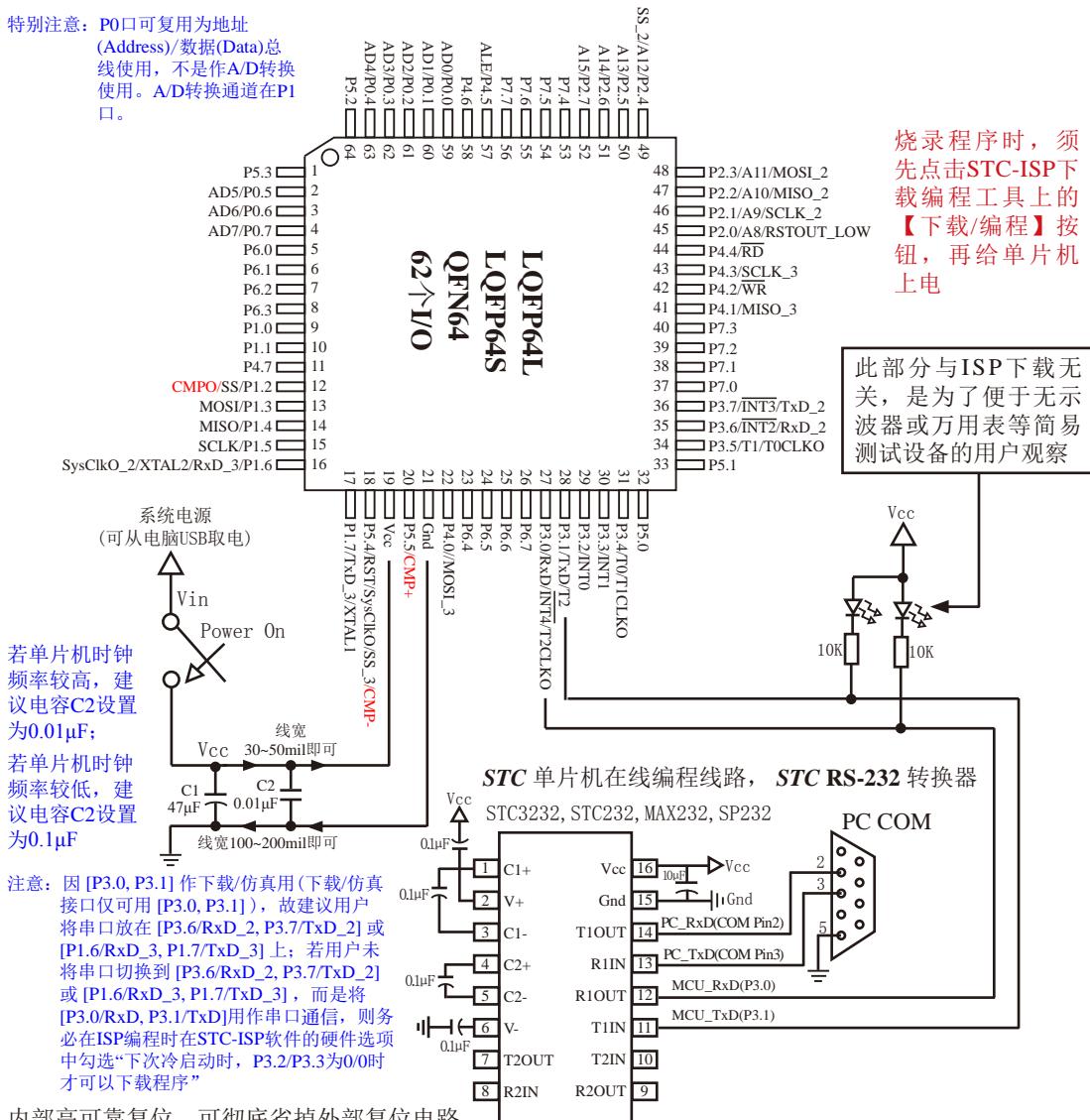

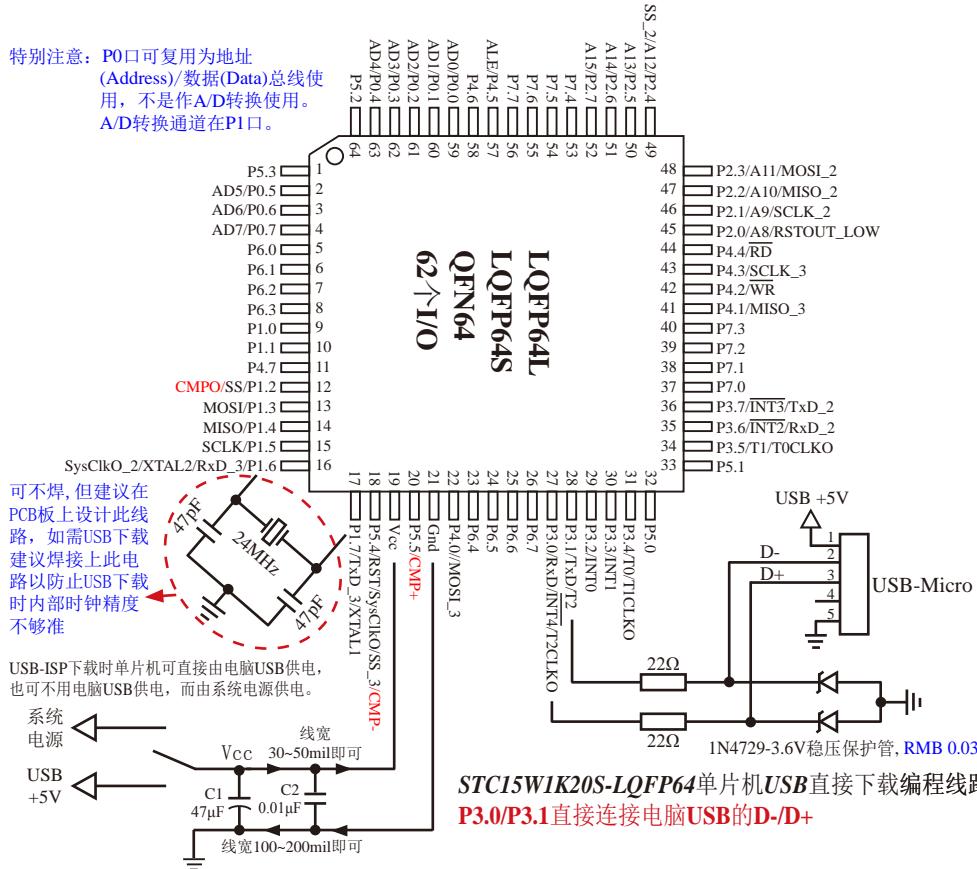

## 6 STC15W1K20S-LQFP64单片机在系统可编程(ISP)典型应用线路图

### 6.1 利用RS-232转换器的ISP下载编程典型应用线路图

特别注意：P0口可复用为地址

(Address)/数据(Data)总线使用，不是作A/D转换使用。A/D转换通道在P1口。

P5.4/RST/SysClkO脚出厂时默认为I/O口，可以通过STC-ISP编程器将其设置为RST复位脚(高电平复位)。

内部集成高精度R/C时钟( $\pm 0.3\%$ )， $\pm 1\%$ 温飘(-40°C ~ +85°C)，常温下温飘 $\pm 0.6\%$ (-20°C ~ +65°C)，5MHz~35MHz宽范围可设置，可彻底省掉外部昂贵的晶振

建议在Vcc和Gnd之间就近加上电源去耦电容C1(47μF), C2(0.01μF), 可去除电源线噪声，提高抗干扰能力

烧录程序时，须先点击STC-ISP下载编程工具上的【下载/编程】按钮，再给单片机上电

此部分与ISP无关，是为了便于示波器或万用表等简易测试设备的用户观察

## 6.2 STC15W1K20S-LQFP64单片机的USB直接下载编程线路, USB-ISP

——单片机的P3.0/P3.1直接连接电脑USB的D-/D+

**特别注意:** P0口可复用为地址

(Address)/数据(Data)总线使

用, 不是作A/D转换使用。

A/D转换通道在P1口。

**注意:** 因 [P3.0, P3.1] 作下载/仿真用(下载/仿真接口仅可用 [P3.0, P3.1]), 故建议用户将串口放在 [P3.6/RxD\_2, P3.7/TxD\_2] 或 [P1.6/RxD\_3, P1.7/TxD\_3] 上; 若用户未将串口切换到 [P3.6/RxD\_2, P3.7/TxD\_2] 或 [P1.6/RxD\_3, P1.7/TxD\_3], 而是将[P3.0/RxD, P3.1/TxD]用作串口通信, 则务必在ISP编程时在STC-ISP软件的硬件选项中勾选“下次冷启动时, P3.2/P3.3为0/0时才可以下载程序”

内部高可靠复位, 可彻底省掉外部复位电路

P5.4/RST/SysClkO脚出厂时默认为I/O口, 可以通过STC-ISP编程器将其设置为RST复位脚(高电平复位)。

建议在Vcc和Gnd之间就近加上电源去耦电容C1(47μF), C2(0.01μF), 可去除电源线噪声, 提高抗干扰能力

### 关于电源:

用户系统的电源可以直接由电脑USB供电, 也可不用电脑USB供电, 而由系统电源供电。

若用户单片机系统直接使用电脑USB供电, 则在用户单片机系统插上电脑USB口时, 电脑就会检测到STC15W1K20S-LQFP64单片机插入到了电脑USB口, 如果用户第一次使用该电脑对STC15W1K20S-LQFP64单片机进行ISP下载, 则该电脑会自动安装USB驱动程序, 而STC15W1K20S-LQFP64单片机则自

动处于等待状态，直到电脑安装完驱动程序并发送【下载/编程】命令给它。

若用户单片机系统使用系统电源供电，则用户单片机系统须在停电(即关闭系统电源)后才能插上电脑USB口；在用户单片机系统插上电脑USB口并打开系统电源后，电脑会检测到STC15W1K20S-LQFP64单片机插入到了电脑USB口，如果用户第一次使用该电脑对STC15W1K20S-LQFP64单片机进行ISP下载，则该电脑会自动安装USB驱动程序，而STC15W1K20S-LQFP64单片机则自动处于等待状态，直到电脑安装完驱动程序并发送【下载/编程】命令给它。

目前，我司针对STC15W1K20S-LQFP64单片机的USB驱动程序只适用于WinXP操作系统及Win7/Win8的32位操作系统，支持Win7/Win8的64操作系统的USB驱动程序尚待进一步开发，建议Win7/Win8的64操作系统使用USB转串口进行ISP下载。

#### 关于晶振：

如果用户单片机系统需用外部晶振，则晶振值必须为24MHz；

如果用户要将用户单片机系统设置成使用内部时钟，则该单片机系统最好不要外接外部晶振；但是如果用户既想将用户单片机系统设置成使用内部时钟，又想外挂外部晶振（24MHz），则该单片机系统上电复位的额外延时<180ms>不能设

USB-Micro 实物图

## 7 STC15W1K20S-LQFP64单片机的管脚说明

| 管脚                             | 管脚编号 | 说明        |                                                                                                                                                         |

|--------------------------------|------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                |      | LQFP64S   | LQFP64L                                                                                                                                                 |

| P0.0/AD0                       | 59   | P0.0      | 标准I/O口 PORT0[0]                                                                                                                                         |

|                                |      | AD0       | 地址/数据总线                                                                                                                                                 |

| P0.1/AD1                       | 60   | P0.1      | 标准I/O口 PORT0[1]                                                                                                                                         |

|                                |      | AD1       | 地址/数据总线                                                                                                                                                 |

| P0.2/AD2                       | 61   | P0.2      | 标准I/O口 PORT0[2]                                                                                                                                         |

|                                |      | AD2       | 地址/数据总线                                                                                                                                                 |

| P0.3/AD3                       | 62   | P0.3      | 标准I/O口 PORT0[3]                                                                                                                                         |

|                                |      | AD3       | 地址/数据总线                                                                                                                                                 |

| P0.4/AD4                       | 63   | P0.4      | 标准I/O口 PORT0[4]                                                                                                                                         |

|                                |      | AD4       | 地址/数据总线                                                                                                                                                 |

| P0.5/AD5                       | 2    | P0.5      | 标准I/O口 PORT0[5]                                                                                                                                         |

|                                |      | AD5       | 地址/数据总线                                                                                                                                                 |

| P0.6/AD6                       | 3    | P0.6      | 标准I/O口 PORT0[6]                                                                                                                                         |

|                                |      | AD6       | 地址/数据总线                                                                                                                                                 |

| P0.7/AD7                       | 4    | P0.7      | 标准I/O口 PORT0[7]                                                                                                                                         |

|                                |      | AD7       | 地址/数据总线                                                                                                                                                 |

| P1.0                           | 9    | P1.0      | 标准I/O口 PORT1[0]                                                                                                                                         |

| P1.1                           | 10   | P1.1      | 标准I/O口 PORT1[1]                                                                                                                                         |

| P1.2/SS/CMPO                   | 12   | P1.2      | 标准I/O口 PORT1[2]                                                                                                                                         |

|                                |      | SS        | SPI同步串行接口的从机选择信号                                                                                                                                        |

| P1.3/MOSI                      | 13   | CMPO      | 比较器的比较结果输出管脚                                                                                                                                            |

|                                |      | P1.3      | 标准I/O口 PORT1[3]                                                                                                                                         |

| P1.4/MISO                      | 14   | MOSI      | SPI同步串行接口的主出从入(主器件的输出和从器件的输入)                                                                                                                           |

|                                |      | P1.4      | 标准I/O口 PORT1[4]                                                                                                                                         |

| P1.5/SCLK                      | 15   | MISO      | SPI同步串行接口的主入从出(主器件的输入和从器件的输出)                                                                                                                           |

|                                |      | P1.5      | 标准I/O口 PORT1[5]                                                                                                                                         |

| P1.6/RxD_3/<br>XTAL2/SysClkO_2 | 16   | SCLK      | SPI同步串行接口的时钟信号                                                                                                                                          |

|                                |      | P1.6      | 标准I/O口 PORT1[6]                                                                                                                                         |

| P1.7/TxD_3/<br>XTAL1           | 17   | RxD_3     | 串口1数据接收端                                                                                                                                                |

|                                |      | SysClkO_2 | 系统时钟输出(输出的频率可为SysClk/1, SysClk/2, SysClk/4, SysClk/16)<br>系统时钟是指对主时钟进行分频后供给CPU、定时器、串行口、SPI的实际工作时钟；主时钟可以是内部R/C时钟，也可以是外部输入的时钟或外部晶体振荡产生的时钟；SysClk是指系统时钟频率。 |

|                                |      | XTAL2     | 内部时钟电路反相放大器的输出端，接外部晶振的其中一端。当直接使用外部时钟源时，此引脚可浮空，此时XTAL2实际将XTAL1输入的时钟进行输出。                                                                                 |

|                                |      | P1.7      | 标准I/O口 PORT1[7]                                                                                                                                         |

|                                |      | TxD_3     | 串口1数据发送端                                                                                                                                                |

|                                |      | XTAL1     | 内部时钟电路反相放大器输入端，接外部晶振的其中一端。当直接使用外部时钟源时，此引脚是外部时钟源的输入端。                                                                                                    |

| 管脚                       | 管脚编号<br>LQFP64S<br>LQFP64L | 说明         |                                                                                                                     |

|--------------------------|----------------------------|------------|---------------------------------------------------------------------------------------------------------------------|

|                          |                            | P2.0       | 标准I/O口 PORT2[0]                                                                                                     |

| P2.0/A8/<br>RSTOUT_LOW   | 45                         | A8         | 地址总线第8位 — A8                                                                                                        |

|                          |                            | RSTOUT_LOW | 上电后,输出低电平,在复位期间也是输出低电平,用户可用软件将其设置为高电平或低电平,如果要读外部状态,可将该口先置高后再读                                                       |

|                          |                            | P2.1       | 标准I/O口 PORT2[1]                                                                                                     |

| P2.1/A9/<br>SCLK_2       | 46                         | A9         | 地址总线第9位 — A9                                                                                                        |

|                          |                            | SCLK_2     | SPI同步串行接口的时钟信号                                                                                                      |

|                          |                            | P2.2       | 标准I/O口 PORT2[2]                                                                                                     |

| P2.2/A10/<br>MISO_2      | 47                         | A10        | 地址总线第10位 — A10                                                                                                      |

|                          |                            | MISO_2     | SPI同步串行接口的主入从出(主器件的输入和从器件的输出)                                                                                       |

|                          |                            | P2.3       | 标准I/O口 PORT2[3]                                                                                                     |

| P2.3/A11/<br>MOSI_2      | 48                         | A11        | 地址总线第11位 — A11                                                                                                      |

|                          |                            | MOSI_2     | SPI同步串行接口的主出从入(主器件的输出和从器件的输入)                                                                                       |

|                          |                            | P2.4       | 标准I/O口 PORT2[4]                                                                                                     |

| P2.4/A12/SS_2            | 49                         | A12        | 地址总线第12位 — A12                                                                                                      |

|                          |                            | SS_2       | SPI同步串行接口的从机选择信号                                                                                                    |

|                          |                            | P2.5       | 标准I/O口 PORT2[5]                                                                                                     |

| P2.5/A13                 | 50                         | A13        | 地址总线第13位 — A13                                                                                                      |

|                          |                            |            |                                                                                                                     |

| P2.6/A14                 | 51                         | P2.6       | 标准I/O口 PORT2[6]                                                                                                     |

|                          |                            | A14        | 地址总线第14位 — A14                                                                                                      |

| P2.7/A15                 | 52                         | P2.7       | 标准I/O口 PORT2[7]                                                                                                     |

|                          |                            | A15        | 地址总线第15位 — A15                                                                                                      |

| P3.0/RxD/INT4<br>/T2CLKO | 27                         | P3.0       | 标准I/O口 PORT3[0]                                                                                                     |

|                          |                            | RxD        | 串口1数据接收端                                                                                                            |

|                          |                            | INT4       | 外部中断4, 只能下降沿中断, INT4支持掉电唤醒                                                                                          |

|                          |                            | T2CLKO     | T2的时钟输出<br>可通过设置INT_CLKO[2]位/T2CLKO将该管脚配置为T2CLKO                                                                    |

| P3.1/TxD/T2              | 28                         | P3.1       | 标准I/O口 PORT3[1]                                                                                                     |

|                          |                            | TxD        | 串口1数据发送端                                                                                                            |

|                          |                            | T2         | 定时器/计数器2的外部输入                                                                                                       |

| P3.2/INT0                | 29                         | P3.2       | 标准I/O口 PORT3[2]                                                                                                     |

|                          |                            | INT0       | 外部中断0, 既可上升沿中断也可下降沿中断.<br>如果IT0(TCON.0)被置为1, INT0管脚仅为下降沿中断。如果IT0(TCON.0)被清0, INT0管脚既支持上升沿中断也支持下降沿中断。<br>INT0支持掉电唤醒。 |

| P3.3/INT1                | 30                         | P3.3       | 标准I/O口 PORT3[3]                                                                                                     |

|                          |                            | INT1       | 外部中断1, 既可上升沿中断也可下降沿中断.<br>如果IT1(TCON.2)被置为1, INT1管脚仅为下降沿中断。如果IT1(TCON.2)被清0, INT1管脚既支持上升沿中断也支持下降沿中断。<br>INT1支持掉电唤醒。 |

| 管脚                       | 管脚编号<br>LQFP64S<br>LQFP64L | 说明          |                                                                            |

|--------------------------|----------------------------|-------------|----------------------------------------------------------------------------|

|                          |                            |             |                                                                            |

| P3.4/T0/T1CLKO           | 31                         | P3.4        | 标准I/O口 PORT3[4]                                                            |

|                          |                            | T0          | 定时器/计数器0的外部输入                                                              |

|                          |                            | T1CLKO      | 定时器/计数器1的时钟输出<br>可通过设置INT_CLKO[1]位/T1CLKO将该管脚配置为T1CLKO，也可对T1脚的外部时钟输入进行分频输出 |

| P3.5/T1/T0CLKO           | 34                         | P3.5        | 标准I/O口 PORT3[5]                                                            |

|                          |                            | T1          | 定时器/计数器1的外部输入                                                              |

|                          |                            | T0CLKO      | 定时器/计数器0的时钟输出<br>可通过设置INT_CLKO[0]位/T0CLKO将该管脚配置为T0CLKO，也可对T0脚的外部时钟输入进行分频输出 |

| P3.6/ <u>INT2</u> /RxD_2 | 35                         | P3.6        | 标准I/O口 PORT3[6]                                                            |

|                          |                            | <u>INT2</u> | 外部中断2, 只能下降沿中断<br><u>INT2</u> 支持掉电唤醒                                       |

|                          |                            | RxD_2       | 串口1数据接收端                                                                   |

| P3.7/ <u>INT3</u> /TxD_2 | 36                         | P3.7        | 标准I/O口 PORT3[7]                                                            |

|                          |                            | <u>INT3</u> | 外部中断3, 只能下降沿中断<br><u>INT3</u> 支持掉电唤醒                                       |

|                          |                            | TxD_2       | 串口1数据发送端                                                                   |

| P4.0/MOSI_3              | 22                         | P4.0        | 标准I/O口 PORT4[0]                                                            |

|                          |                            | MISO_3      | SPI同步串行接口的主入从出(主器件的输入和从器件的输出)                                              |

| P4.1/MISO_3              | 41                         | P4.1        | 标准I/O口 PORT4[1]                                                            |

|                          |                            | MOSI_3      | SPI同步串行接口的主出从入(主器件的输出和从器件的输入)                                              |

| P4.2/ <u>WR</u>          | 42                         | P4.2        | 标准I/O口 PORT4[2]                                                            |

|                          |                            | <u>WR</u>   | 外部数据存储器写脉冲                                                                 |

| P4.3/SCLK_3              | 43                         | P4.3        | 标准I/O口 PORT4[3]                                                            |

|                          |                            | SCLK_3      | SPI同步串行接口的时钟信号                                                             |

| P4.4/ <u>RD</u>          | 44                         | P4.4        | 标准I/O口 PORT4[4]                                                            |

|                          |                            | <u>RD</u>   | 外部数据存储器读脉冲                                                                 |

| P4.5/ALE                 | 57                         | P4.5        | 标准I/O口 PORT4[5]                                                            |

|                          |                            | ALE         | 地址锁存允许                                                                     |

| P4.6                     | 58                         | P4.6        | 标准I/O口 PORT4[6]                                                            |

| P4.7                     | 11                         | P4.7        | 标准I/O口 PORT4[7]                                                            |

| P5.0                     | 32                         | P5.0        | 标准I/O口 PORT5[0]                                                            |

| P5.1                     | 33                         | P5.1        | 标准I/O口 PORT5[1]                                                            |

| P5.2                     | 64                         | P5.2        | 标准I/O口 PORT5[2]                                                            |

| 管脚                                 | 管脚编号<br>LQFP64 | 说明              |                                                                                                                                                         |

|------------------------------------|----------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| P5.3                               | 1              | P5.3            | 标准I/O口 PORT5[3]                                                                                                                                         |

| P5.4/RST/<br>SysClkO/<br>SS_3/CMP- | 18             | P5.4            | 标准I/O口 PORT5[4]                                                                                                                                         |

|                                    |                | RST             | 复位脚(高电平复位)                                                                                                                                              |

|                                    |                | SysClkO         | 系统时钟输出(输出的频率可为SysClk/1, SysClk/2, SysClk/4, SysClk/16)<br>系统时钟是指对主时钟进行分频后供给CPU、定时器、串行口、SPI的实际工作时钟；主时钟可以是内部R/C时钟，也可以是外部输入的时钟或外部晶体振荡产生的时钟；SysClk是指系统时钟频率。 |

|                                    |                | SS_3            | SPI同步串行接口的从机选择信号                                                                                                                                        |

|                                    |                | CMP-            | 比较器负极输入端 (若该口被用作比较器负极，则该口需被设置为高阻输入)                                                                                                                     |

|                                    |                | P5.5            | 标准I/O口 PORT5[5]                                                                                                                                         |

| P5.5/CMP+                          | 20             | CMP+            | 比较器正极输入端(若该口被用作比较器正极，则该口需被设置为高阻输入)                                                                                                                      |

| P6.0                               | 5              | 标准I/O口 PORT6[0] |                                                                                                                                                         |

| P6.1                               | 6              | 标准I/O口 PORT6[1] |                                                                                                                                                         |

| P6.2                               | 7              | 标准I/O口 PORT6[2] |                                                                                                                                                         |

| P6.3                               | 8              | 标准I/O口 PORT6[3] |                                                                                                                                                         |

| P6.4                               | 23             | 标准I/O口 PORT6[4] |                                                                                                                                                         |

| P6.5                               | 24             | 标准I/O口 PORT6[5] |                                                                                                                                                         |

| P6.6                               | 25             | 标准I/O口 PORT6[6] |                                                                                                                                                         |

| P6.7                               | 26             | 标准I/O口 PORT6[7] |                                                                                                                                                         |

| P7.0                               | 37             | 标准I/O口 PORT7[0] |                                                                                                                                                         |

| P7.1                               | 38             | 标准I/O口 PORT7[1] |                                                                                                                                                         |

| P7.2                               | 39             | 标准I/O口 PORT7[2] |                                                                                                                                                         |

| P7.3                               | 40             | 标准I/O口 PORT7[3] |                                                                                                                                                         |

| P7.4                               | 53             | 标准I/O口 PORT7[4] |                                                                                                                                                         |

| P7.5                               | 54             | 标准I/O口 PORT7[5] |                                                                                                                                                         |

| P7.6                               | 55             | 标准I/O口 PORT7[6] |                                                                                                                                                         |

| P7.7                               | 56             | 标准I/O口 PORT7[7] |                                                                                                                                                         |

| Vcc                                | 19             | 电源正极            |                                                                                                                                                         |

| Gnd                                | 21             | 电源负极，接地         |                                                                                                                                                         |

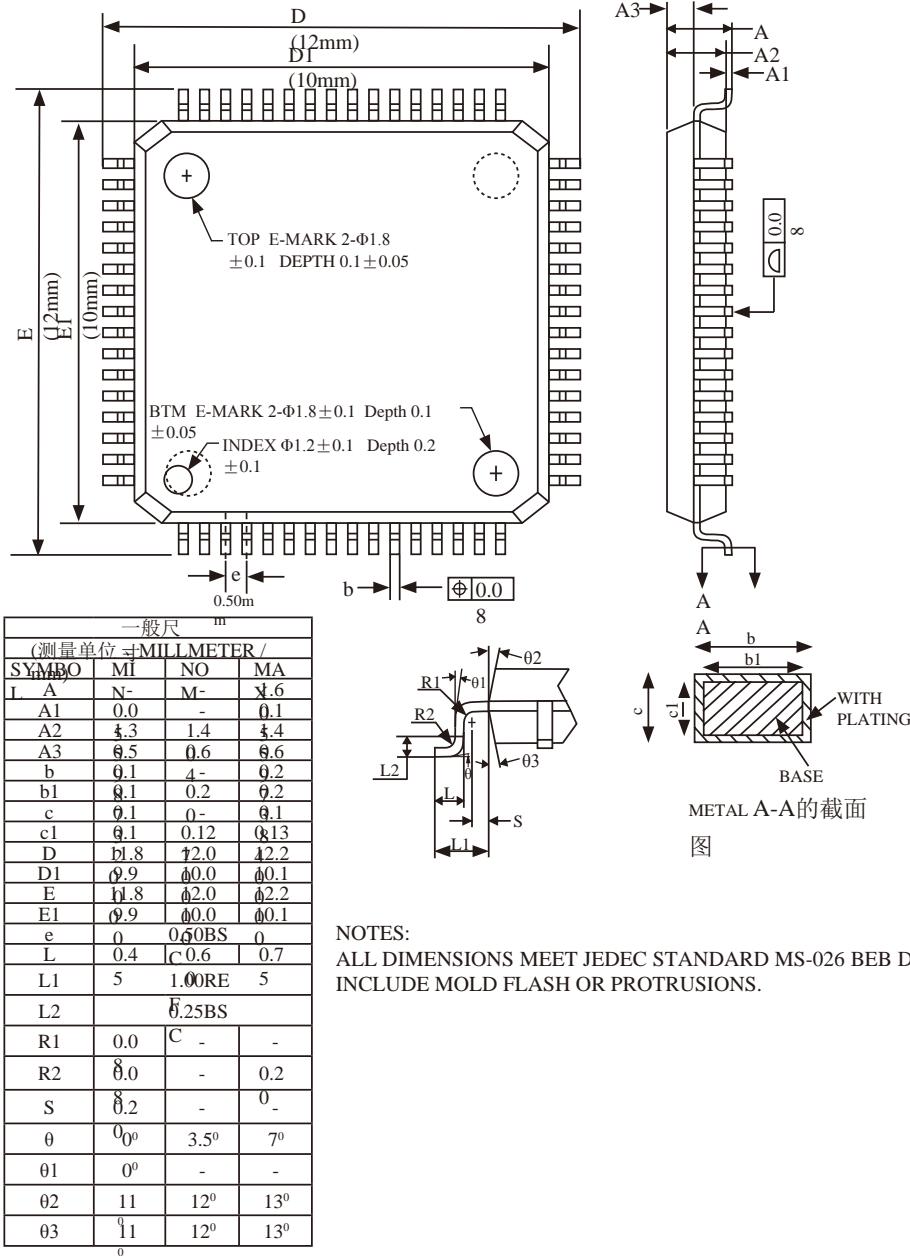

## 8 STC15系列单片机封装尺寸图

### 8.1 LQFP64S封装尺寸图

LQFP64 SMALL OUTLINE PACKAGE (LQFP64S)

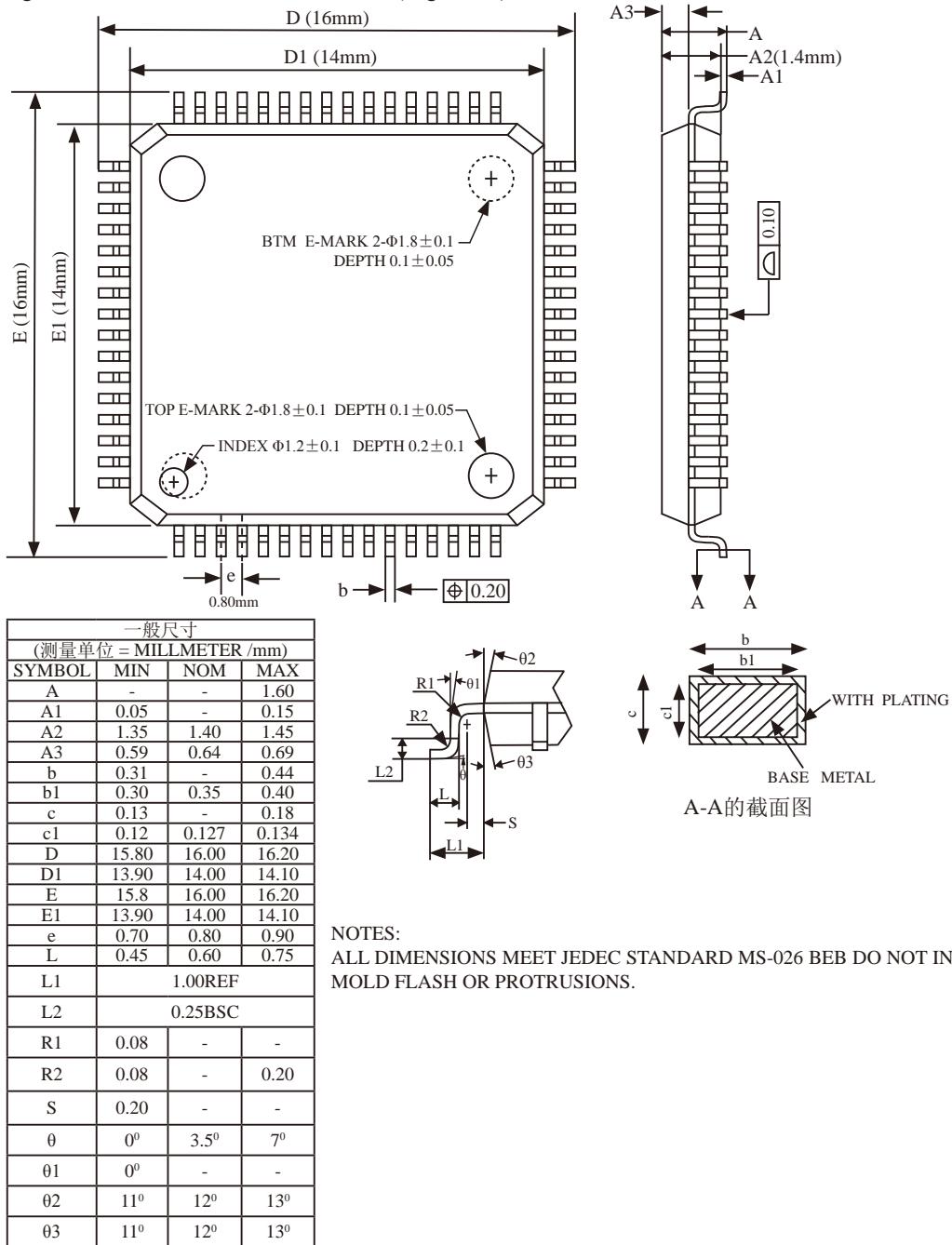

## 8.2 LQFP64L封装尺寸(16mm x 16mm)图

## LQFP64 LARGE OUTLINE PACKAGE (LQFP64L)

## NOTES.

ALL DIMENSIONS MEET JEDEC STANDARD MS-026 BEB DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS